US008073027B2

# (12) United States Patent

Deladurantaye et al.

# (54) DIGITAL LASER PULSE SHAPING MODULE AND SYSTEM

(75) Inventors: **Pascal Deladurantaye**, Lévis (CA); **François Duchesne**, Québec (CA);

Michel Jacob, Québec (CA); Yvan Mimeault, Québec (CA); André Parent,

Québec (CA); **Yves Taillon**, Saint-Augustin de Desmaures (CA)

(73) Assignee: Institut National d'Optique, Quebec

(CA)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 267 days.

(21) Appl. No.: 12/493,949

(22) Filed: Jun. 29, 2009

(65) **Prior Publication Data**

US 2009/0323741 A1 Dec. 31, 2009

### Related U.S. Application Data

- (60) Provisional application No. 61/076,337, filed on Jun. 27, 2008.

- (51) **Int. Cl.** *H01S 3/13* (2006.01)

- (52) **U.S. Cl.** ...... **372/29.014**; 372/29.01; 372/25; 372/9

## (56) References Cited

### U.S. PATENT DOCUMENTS

5,151,909 A 9/1992 Davenport et al. 5,226,051 A 7/1993 Chan et al.

# (10) Patent No.: US 8,073,027 B2 (45) Date of Patent: Dec. 6, 2011

| 6,172,325    | B1            | 1/2001  | Baird et al.         |            |

|--------------|---------------|---------|----------------------|------------|

| 6,281,471    | B1            | 8/2001  | Smart                |            |

| 6,477,107    | B1 *          | 11/2002 | Lee                  | 365/233.18 |

| 7,126,746    | B2            | 10/2006 | Sun et al.           |            |

| 7,348,516    | B2            | 3/2008  | Sun et al.           |            |

| 2006/0159138 | $\mathbf{A}1$ | 7/2006  | Deladurantaye et al. |            |

| 2007/0228024 | A1            | 10/2007 | Bruland et al.       |            |

| 2007/0248136 | A1            | 10/2007 | Leonardo et al.      |            |

| 2008/0013163 | $\mathbf{A}1$ | 1/2008  | Leonardo et al.      |            |

| 2008/0080570 | A1            | 4/2008  | Murison et al.       |            |

| 2008/0225935 | A1            | 9/2008  | Reddy                |            |

| 2008/0233715 | A1            | 9/2008  | Liu et al.           |            |

| 2008/0261382 | A1            | 10/2008 | Starodoumov et al.   |            |

| 2008/0310568 | A1            | 12/2008 | Sander               |            |

| 2009/0010288 | $\mathbf{A}1$ | 1/2009  | Keaton et al.        |            |

|              |               |         |                      |            |

### FOREIGN PATENT DOCUMENTS

WO WO 2008/014331 A2 1/2008 WO WO 2009/155712 A1 12/2009

### OTHER PUBLICATIONS

Koechner, "Solid-State laser engineering", Springer-Verlag, Chapter 8, figure 8.8.

\* cited by examiner

Primary Examiner — Kinam Park (74) Attorney, Agent, or Firm — Merchant & Gould P.C.

#### (57) ABSTRACT

A digital pulse shaping module for controlling a pulsed laser oscillator according to a digital input waveform is provided. The pulse shaping module includes a clock generator generating a plurality of phase-related clock signals and a shape generator which outputs a digital shape signal corresponding to the digital input waveform in Double Data Rate in response to the clock signals. A DAC converts the digital shape into an analog shape signal. The analog shape signal may be used to control the current source of a laser seed source or modulators in the laser oscillator shaping a seed light signal. Optionally, the pulse shaping module may also output a gate control signal having a predetermined timing relationship with respect to the digital shape signal.

# 40 Claims, 38 Drawing Sheets

FIG. 2

FIG. 6

FIG. 7

FIG. 16

FIG. 17

FIG. 20

FIG. 21

FIG. 22

FIG. 23

FIG. 25

FIG. 26

FIG. 39

FIG. 41

# DIGITAL LASER PULSE SHAPING MODULE AND SYSTEM

This application claims benefit of Ser. No. 61/076,337, filed 27 Jun. 2008 in the United States and which application 5 is incorporated herein by reference. To the extent appropriate, a claim of priority is made to the above disclosed application.

## FIELD OF THE INVENTION

The present invention relates to the field of laser devices and more particularly concerns a digital platform for providing pulse shaping control signals to a laser oscillator.

#### **BACKGROUND**

Many industrial fields require laser processing capability and for such applications, the primary concern is often to generate optical laser pulses with, to some extent, real-time control over the pulse amplitude, duration, shape, peak power 20 and repetition rate. In some applications, such as laser-based material-processing, the rise time and fall time of the shaped optical pulses are also important functional specifications.

U.S. Pat. No. 7,348,516 (SUN et al.), entitled "Methods of and laser systems for link processing using laser pulses with 25 specially tailored power profiles" presents many arguments in favor of pulsed laser systems providing fine control over the pulse temporal power profile in the nanosecond regime, for facilitating better link process quality and yield. Three different laser architectures providing a certain control over the 30 laser pulse shapes are described therein. U.S. Pat. No. 7,126, 746 (SUN et al.) further teaches a laser system providing control over the pulse shapes and having a Master Oscillator Power Amplifier (MOPA) configuration. A practical manner of digitally generating appropriate control signals for such 35 systems is not however described in either document.

U.S. Pat. No. 6,281,471 (SMART), entitled "Energy-efficient, laser-based method and system for processing target material" describes many requirements and specifications concerning the temporal generation of square laser pulse 40 shapes in material processing. The system presented therein includes, among its main components, a controller for generating a processing control signal, and a signal generator for generating a modulated drive waveform based on the processing control signal. SMART however does not tackle the issue 45 of the implementation or integration of the controller and the waveform generator into the system described.

Optical pulse shaping implementation can originate from digital electronic means, where some electronic apparatus reads a given sequence of digital samples previously stored in 50 a memory buffer, and writes these samples into a digital-toanalog converter (DAC). The shaped analog signal output by the DAC is then fed to a buffer amplifier having enough bandwidth and drive capability for directly modulating a light source such as a laser diode, or driving an electro-optic modu- 55 pulse shaping module are embedded in a high speed digital

U.S. Patent Application Publication No. 2008/0080,570 (MURISON et al.), entitled "Method and system for a pulsed laser source emitting shaped optical waveforms" presents a tunable pulsed laser source where optical pulse shaping is 60 based on the digital approach just described above. This pulsed laser architecture implements a double-pass optical fibre amplifier that uses a single Mach-Zehnder type amplitude modulator. The electrical analog shaping signal drives two successive openings of the optical modulator. MURI-SON also emphasized that electrical pulse shaping capability is beneficial for the reduction of gain saturation in the fiber

2

amplifier, or for several fields of laser processing where it is desirable that the optical pulse be different than a square pulse. Although MURISON mentions that the shaped waveform originates from a digital pattern stored in memory onboard a DAC, it does not provide an explicit architecture or method for transferring data from the memory to the DAC. apart from using built-in functional features of an off-theshelf laboratory instrument such as the AWG2040 (trademark) waveform generator from Tektronix Inc.

Other architectures than the one described by MURISON exist for building pulsed laser sources and these architectures may benefit from the advantages of optical pulse shaping produced from digital electronics as well. An example is U.S. Pat Application published under No. US2006/0159138 (DELADURANTAYE et al.), entitled "Pulse laser light source". This patent application describes a pulse laser source built around two Mach-Zehnder modulators. In the general case of this architecture, it is likely that distinct analog pulse shaping signals must be generated for each modulator, along with proper synchronization and delay settings between one and the other.

Finally, pulsed laser sources sometimes necessitate that several utilitarian functions or modes of operations be present in or in close vicinity of the main architectural body of the fiber amplifier. Typical examples of such functions or modes of operations are a bias servo function for maintaining the extinction point of an electro-optic modulator, the on-demand generation of a quasi-CW optical output or the monitoring and control of the laser pump drivers. In those approaches where individual stand-alone waveform generators and controlling electronics are used, timing jitter as well as synchronization aspects must be carefully managed. In general, such approaches result in higher system cost, volume and complexity.

There is therefore a need for a digital module for generating appropriate control signals for a pulsed laser oscillator.

## SUMMARY OF THE INVENTION

In accordance with a first aspect of the present invention, there is provided a digital pulse shaping module for controlling a pulsed laser oscillator according to a digital input waveform, comprising:

- a clock generator generating a plurality of phase-related clock signals at a same clock frequency;

- a shape generator outputting a digital shape signal corresponding to said digital input waveform, said shape generator operating in Double Data Rate in response to said clock signals; and

- a Digital-to-Analog Converter, hereinafter DAC, receiving the digital shape signal and converting the same into an analog shape signal.

Preferably, at least part of the components of the digital logic circuit, such as for example a FPGA or an ASIC.

In accordance with another aspect of the present invention, the digital pulse shaping module is provided in combination with a connector interface interfacing communication between the digital pulse shaping module and user equip-

In accordance with yet another aspect of the invention, there is also provided a pulse laser system for generating laser pulses, said pulsed laser system comprising:

- a digital pulse shaping module comprising:

- a clock generator generating a plurality of phase-related clock signals at a same clock frequency;

- a shape generator outputting a digital shape signal corresponding to said digital input waveform, said shape generator operating in Double Data Rate in response to said clock signals;

- a Digital-to-Analog Converter, hereinafter DAC, receiving the digital shape signal and converting the same into an analog shape signal; and

- a shape buffer driver receiving the analog shape signal and generating a control shape signal; and

- a laser oscillator receiving said control shape signal and 10 generating said laser pulses in accordance therewith.

The laser oscillator may be based, for example, on a continuous seed light source pulsed by modulators controlled by the digital pulse shaping module, or on a pulsed seed light source whose current source is directly controlled by this 15 module.

## BRIEF DESCRIPTION OF THE DRAWINGS

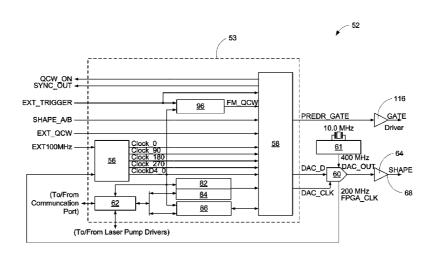

- FIG. 1 is a schematic representation of a pulsed laser system which includes a digital pulse shaping module according to an embodiment of the invention.

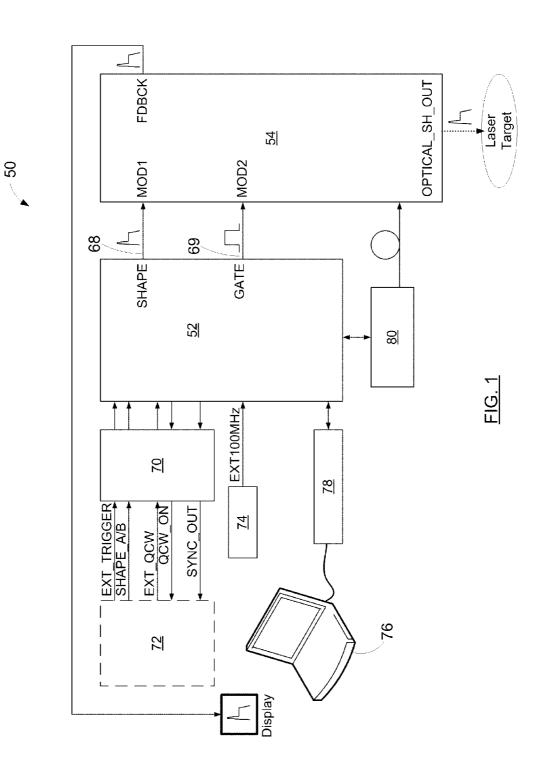

- FIG. 2 is a graph illustrating the timing relationships between input and output signals of the digital pulse shaping module of FIG. 1.

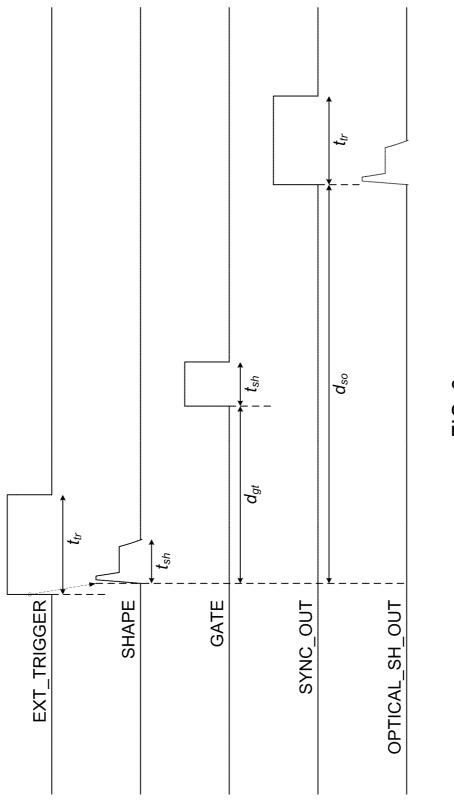

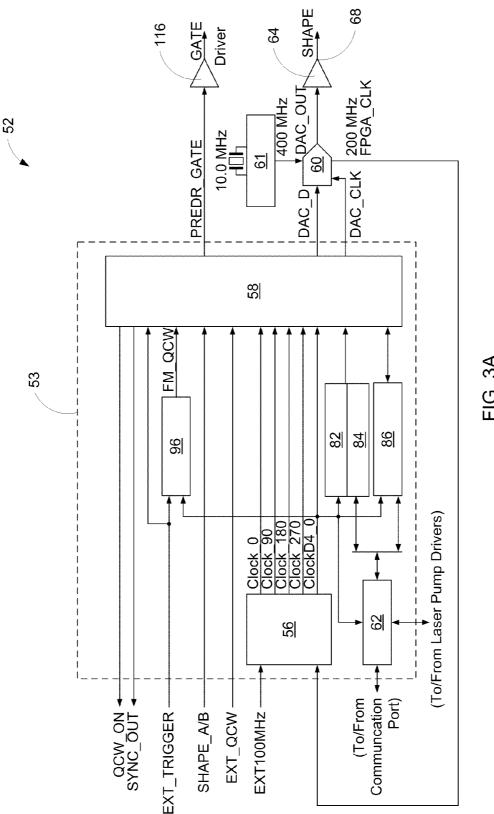

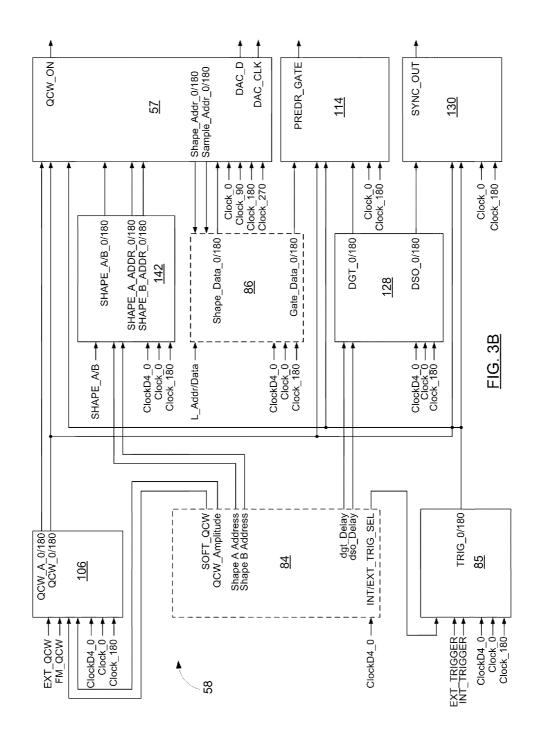

- FIG. 3A is a block diagram of a digital pulse shaping module according to an embodiment of the invention; FIG. 3B is a block diagram of the shape generator of the digital pulse shaping module of FIG. 3A.

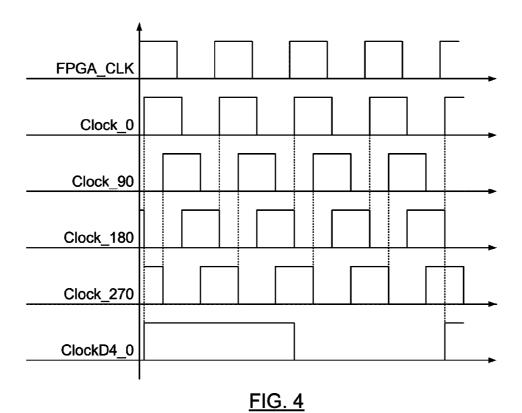

- FIG. 4 is a graph schematically illustrating the phase-30 related clock signals outputted by the clock generator according to a preferred embodiment of the invention.

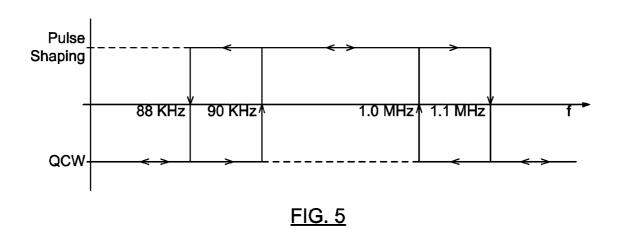

- FIG.  $\hat{\mathbf{5}}$  shows a hysteresis output transition diagram for the frequency measurement module of the digital pulse shaping module of FIG.  $\mathbf{3}$ .

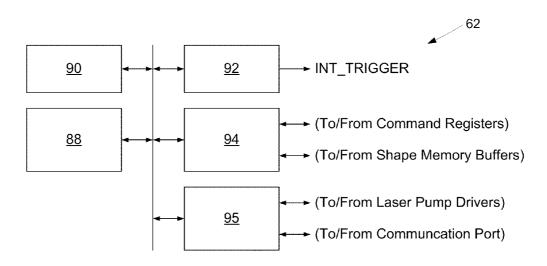

- FIG. 6 schematically illustrates the architecture of an embedded microcontroller according to one embodiment of the invention.

- FIG. 7 schematically illustrates a command read/write register set according to an embodiment.

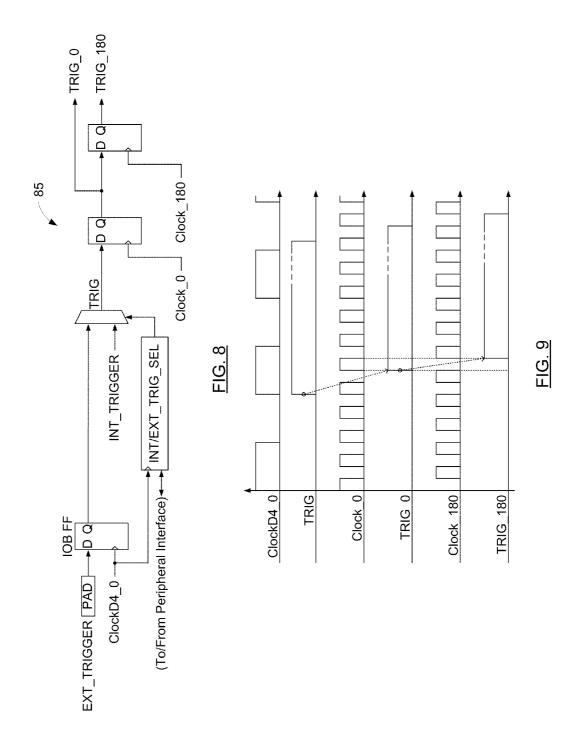

- FIG. **8** schematically illustrates a DDR implementation of an internal/external pulse trigger.

- FIG. 9 is a timing diagram showing signal synchronization from the 50 MHz to the 200 MHz time-critical clock domains.

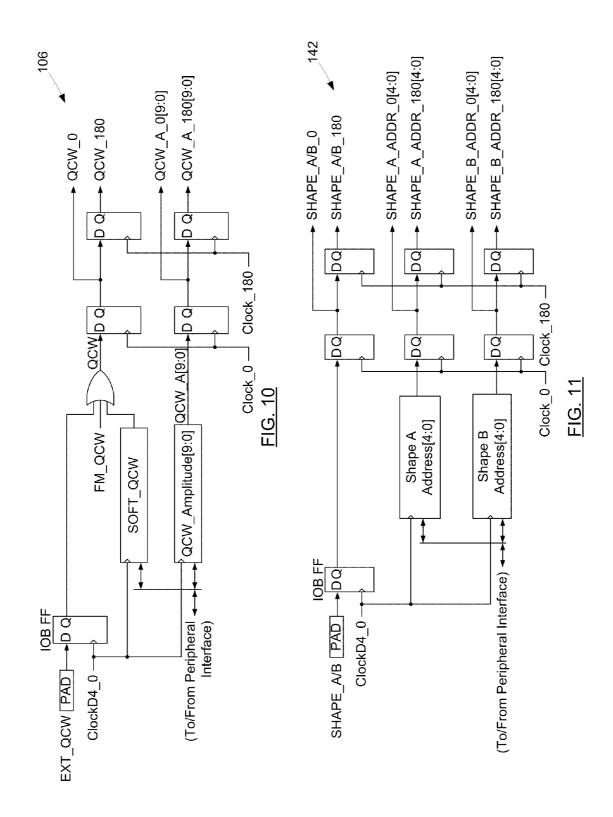

- FIG. 10 schematically illustrates the DDR implementation 45 of a QCW control sub-module according to an embodiment of the invention.

- FIG. 11 schematically illustrates the DDR implementation of a shape selection sub-module according to an embodiment of the invention.

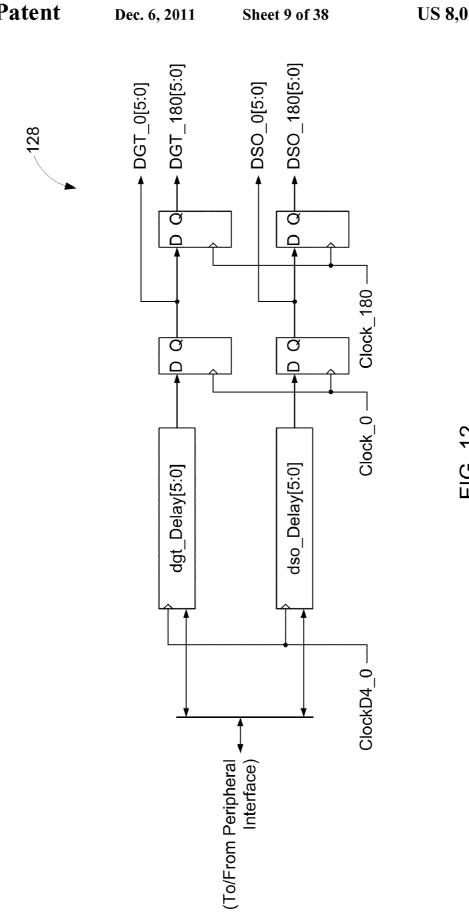

- FIG. 12 schematically illustrates the DDR implementation of a delay control sub-module according to an embodiment of the invention.

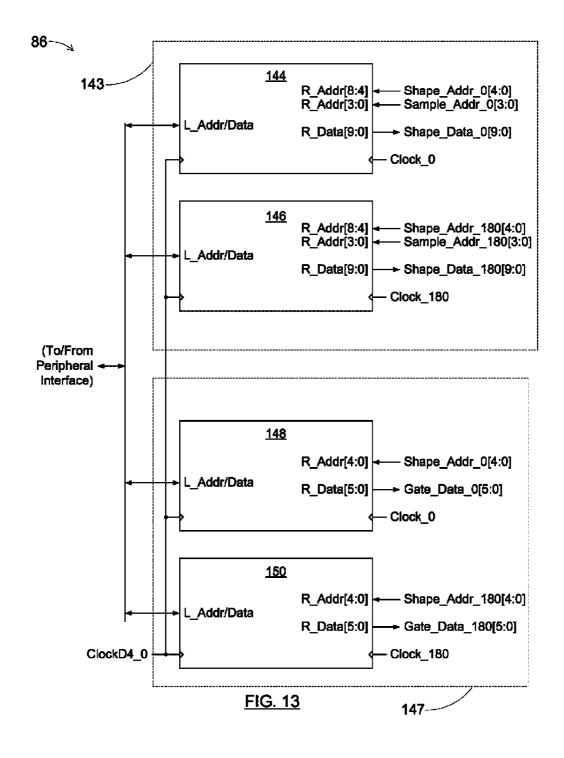

- FIG. 13 schematically illustrates a dual-port pulse shape memory buffer.

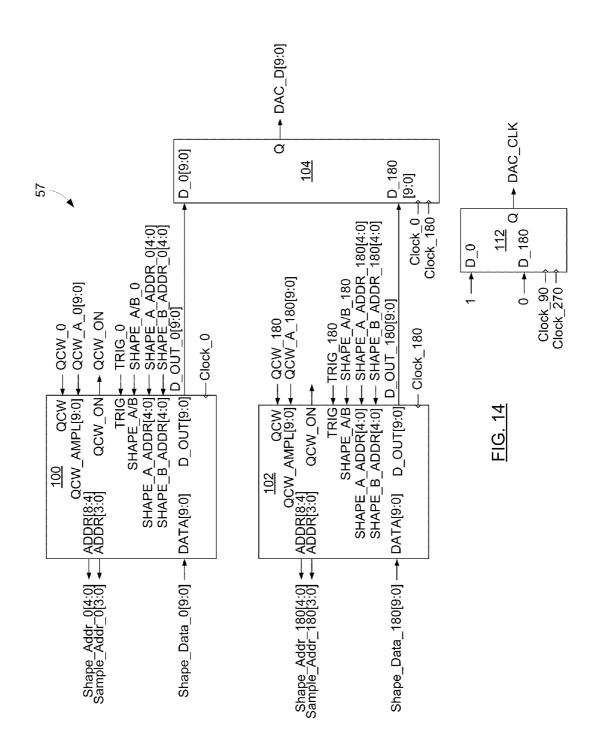

- FIG. 14 is a block diagram of a shape sub-module according to an embodiment of the invention.

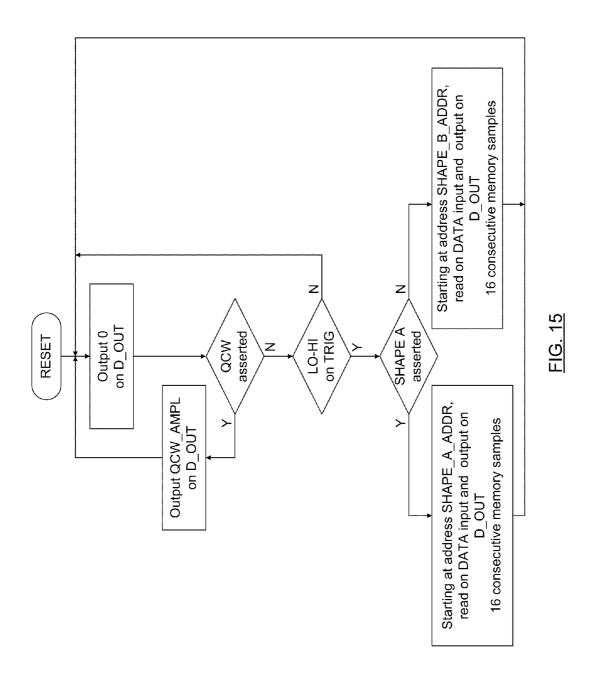

- FIG. 15 is a logic flow chart of the operation of a shape state machine according to the embodiment of FIG. 14.

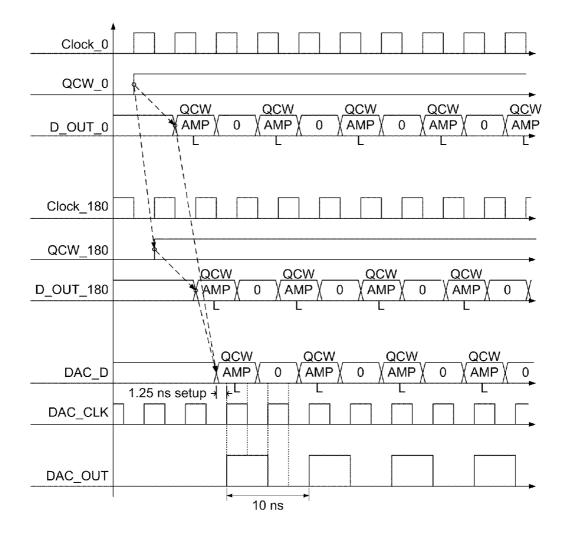

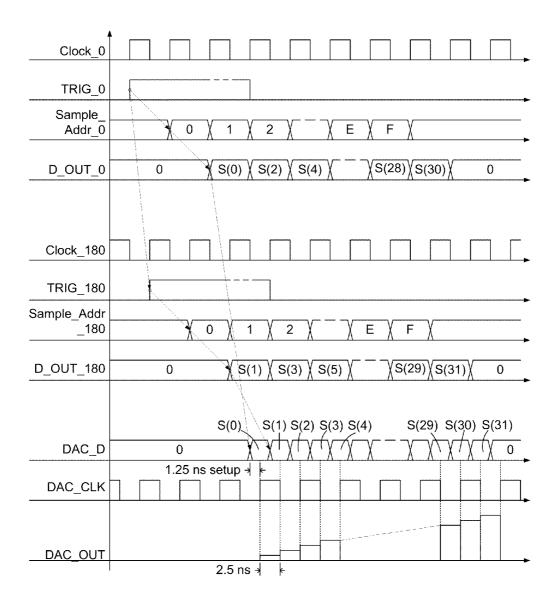

- FIG. 16 is a timing diagram for the DDR generation of the 60 100 MHz QCW.

- FIG. 17 is a timing diagram for the DDR generation of a user-defined arbitrary pulse shape.

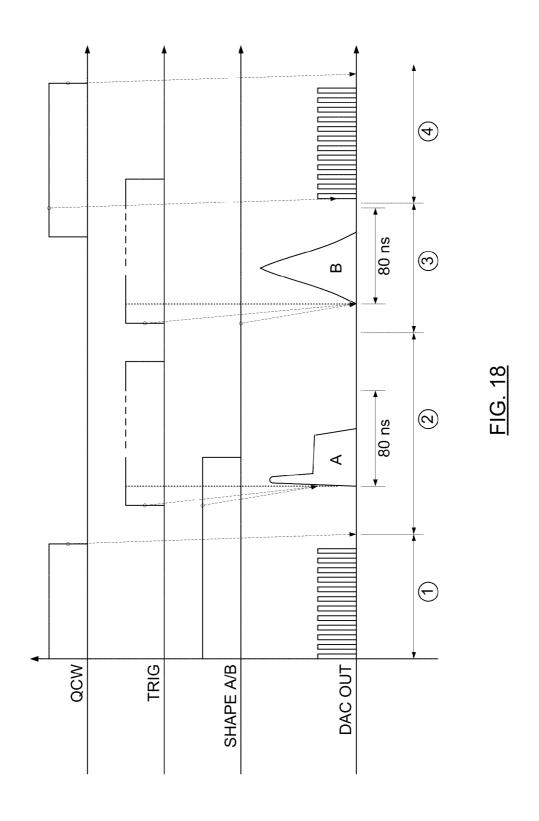

- FIG. 18 is a typical timing diagram of mode switching and pulse shape switching.

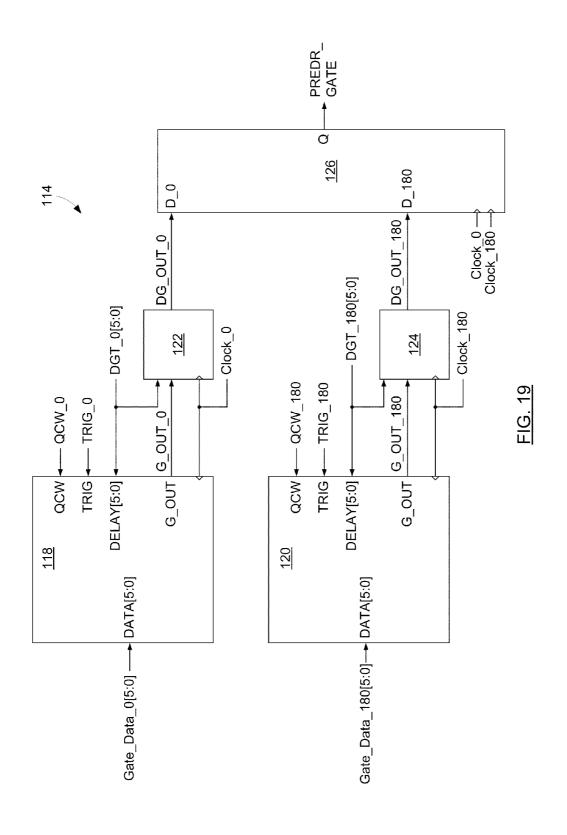

- FIG.  $1\overline{9}$  is a block diagram of a gate sub-module according to an embodiment of the invention.

4

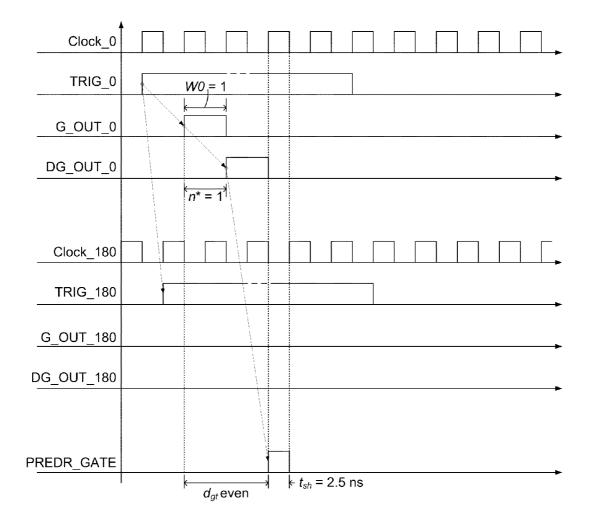

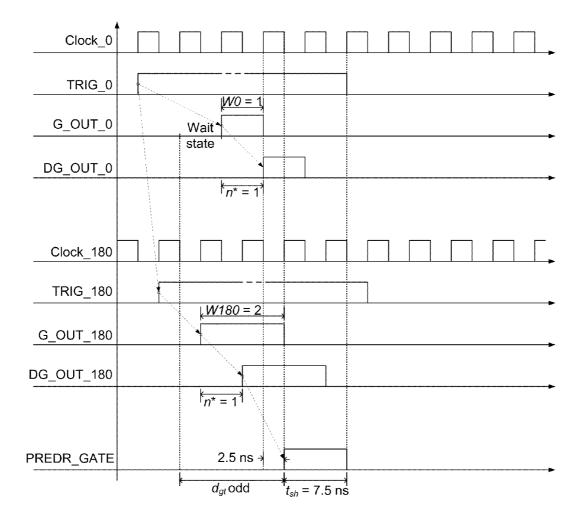

- FIG. **20** is a timing diagram schematically illustrating the DDR PREDR\_GATE output for w odd, n even.

- FIG. **21** is a timing diagram schematically illustrating the DDR PREDR\_GATE output for w odd, n odd.

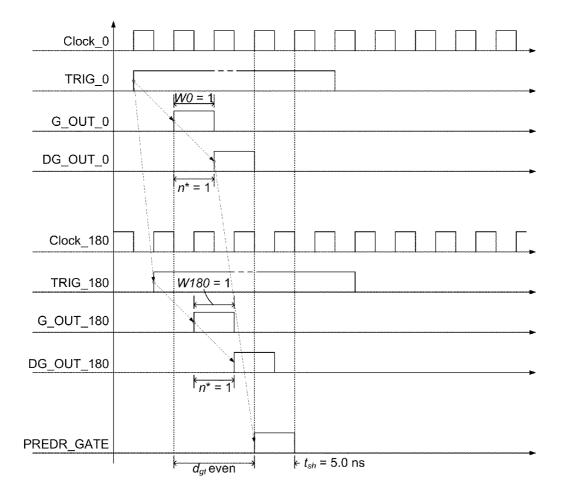

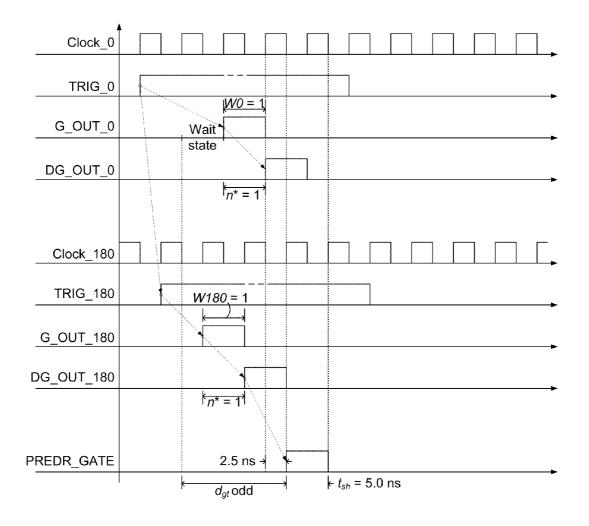

- FIG. **22** is a timing diagram schematically illustrating the DDR PREDR\_GATE output for w even, n even.

- FIG. 23 is a timing diagram schematically illustrating the DDR PREDR\_GATE output for w even, n odd.

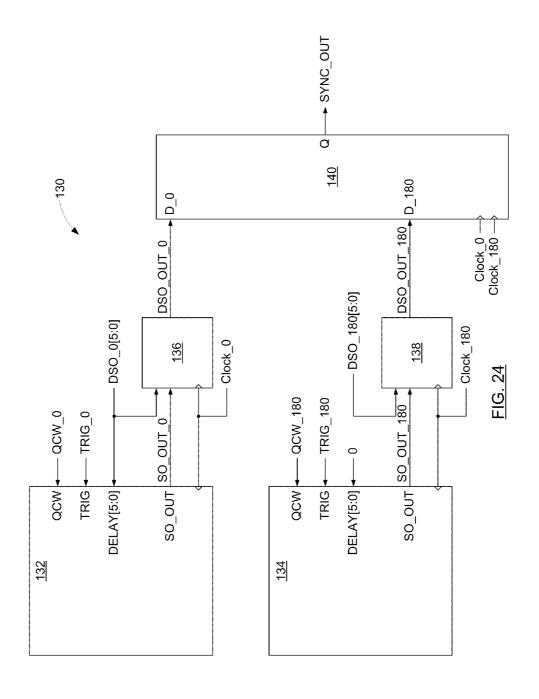

- FIG. **24** is a block diagram of the synchronization submodule according to an embodiment of the invention.

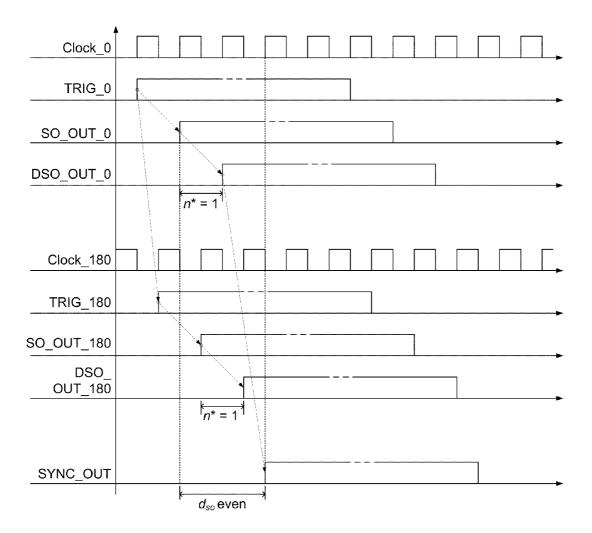

- FIG. **25** is a timing diagram schematically illustrating the DDR SYNC\_OUT output for n even.

- FIG. **26** is a timing diagram schematically illustrating the DDR SYNC\_OUT output for n odd.

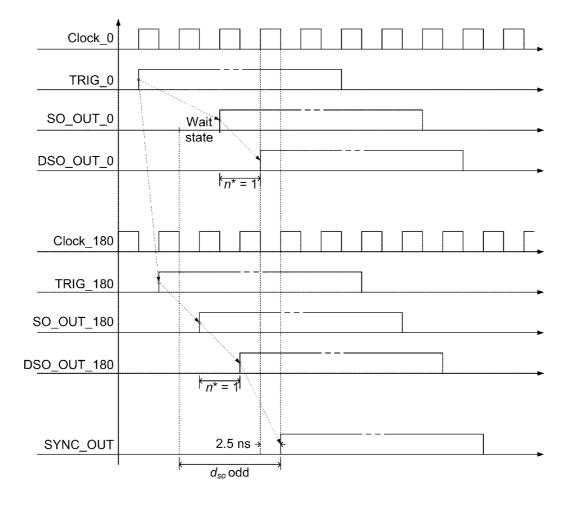

- FIG. 27 schematically illustrates an embodiment of the present invention including a pulsed laser source employing two electro-optic modulators and a seed laser diode operated in the CW regime.

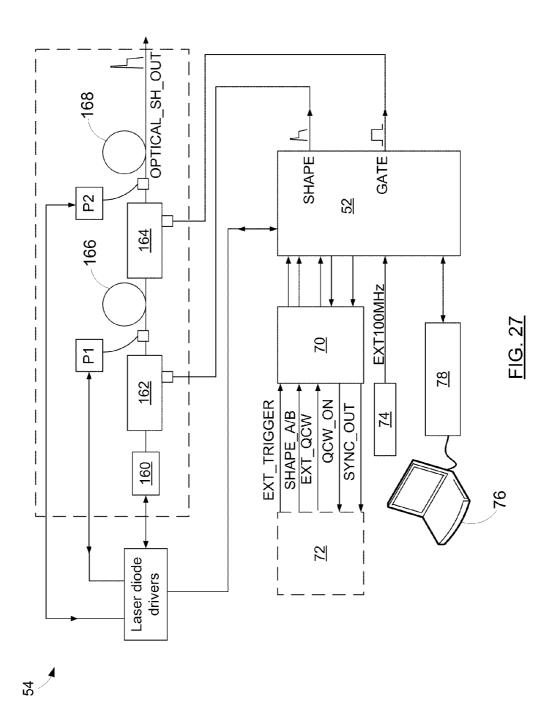

- FIG. 28 schematically illustrates the pulsed laser source emission wavelength tuning for amplification in a solid state optical amplifier.

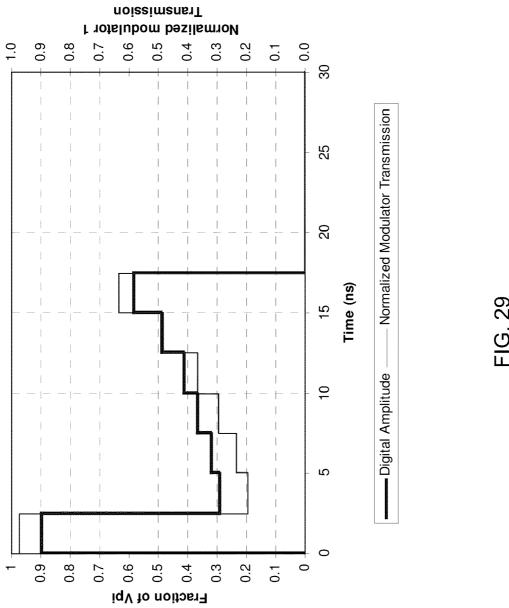

- FIG. 29 shows an example of optical shape at the output of the first modulator corresponding to a particular digital waveform (SHAPE signal).

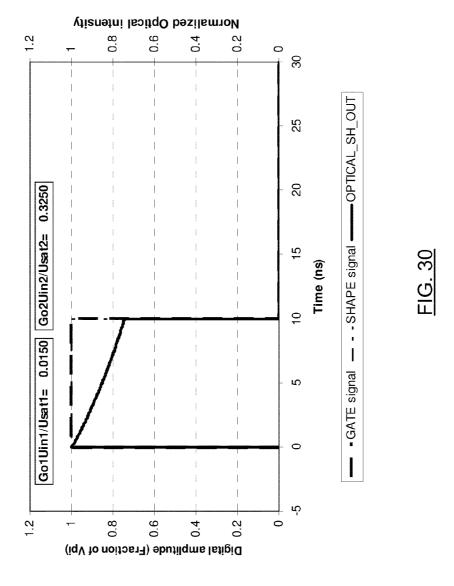

- FIG. 30 shows a typical pulse shape distortion resulting from optical gain saturation for rectangular SHAPE and GATE waveforms.

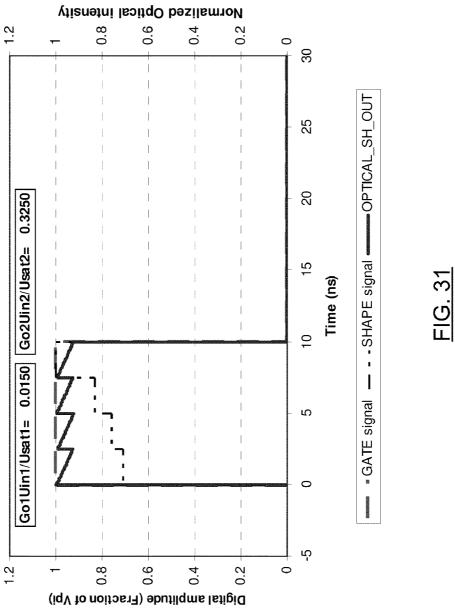

- FIG. 31 shows an example of rectangular optical shape (OPTICAL\_SH\_OUT) obtained through appropriate adjustment of the different amplitudes values of the SHAPE signal so as to compensate optical gain saturation.

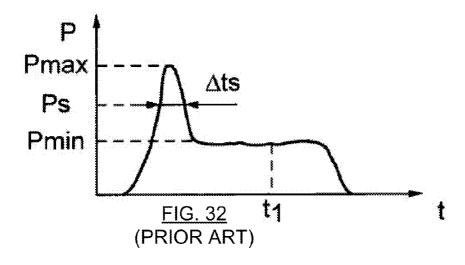

- FIG. **32** [PRIOR ART] shows the prior art optical pulse shape for link severing, with a spike at the leading edge of the pulse.

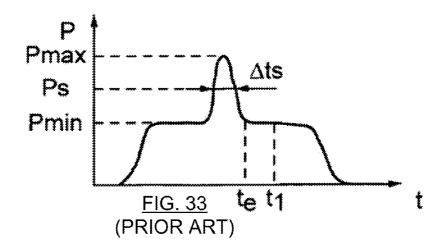

- FIG. 33 [PRIOR ART] shows the prior art optical pulse shape for link severing, with a spike appearing during the laser pulse.

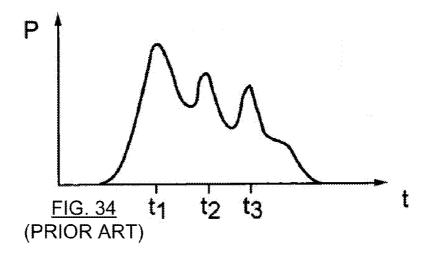

- FIG. 34 [PRIOR ART] shows the prior art optical pulseshape for link severing, with multiple spikes appearing during the laser pulse.

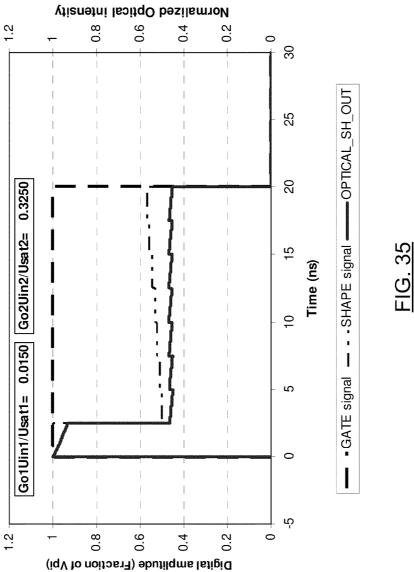

- FIG. 35 shows an example of optical shape obtained with an embodiment of the present invention, corresponding to the optical shape type presented at FIG. 32.

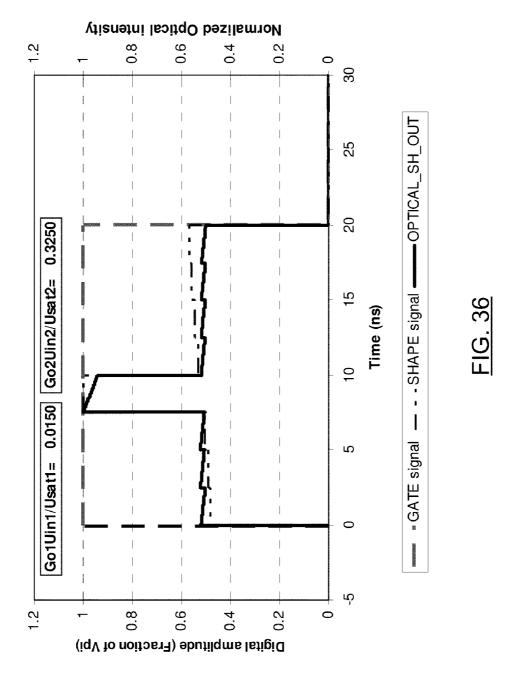

- FIG. 36 shows an example of optical shape obtained with an embodiment of the present invention, corresponding to the optical shape type presented at FIG. 33.

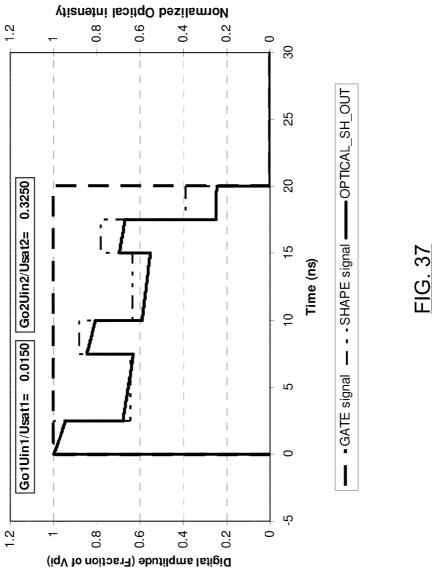

- FIG. 37 shows an example of optical shape obtained with an embodiment of the present invention, corresponding to the optical shape type presented at FIG. 34.

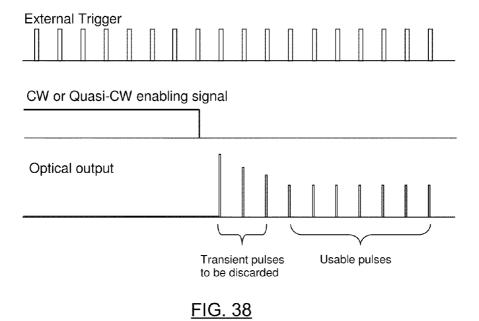

- FIG. **38** is an illustration of the transient response of conventional pulsed lasers when switching from the CW or quasi-CW mode to the pulsed mode.

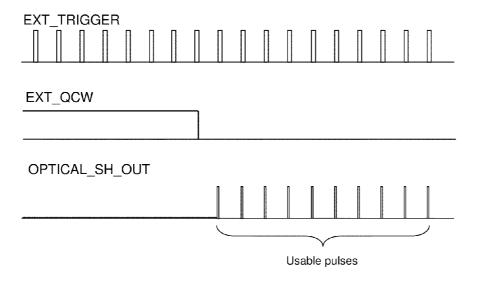

- FIG. **39** is an illustration of the transient response that can 55 be obtained with an embodiment of the present invention.

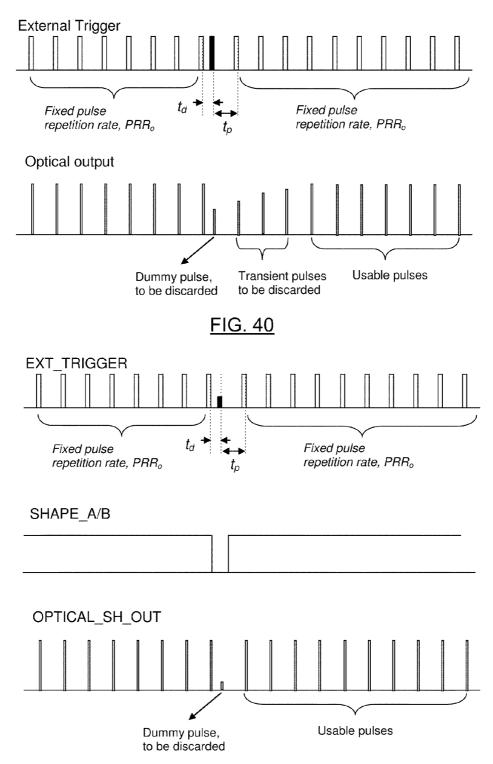

- FIG. 40 is an illustration of the transient response of conventional pulsed lasers when inserting a dummy pulse.

- FIG. 41 is an illustration of the benefits of the pulse shape agility according to an embodiment of the present invention for alleviating the throughput penalty arising from the laser transient response when inserting a dummy pulse.

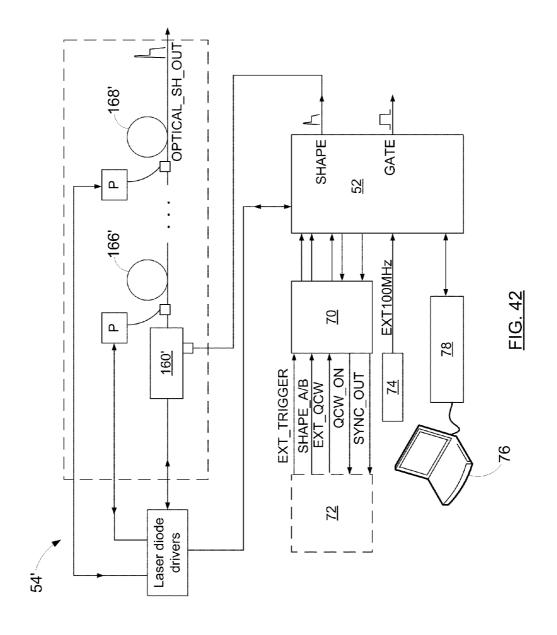

- FIG. 42 schematically illustrates an embodiment of the present invention using a seed laser diode operated in the pulsed regime.

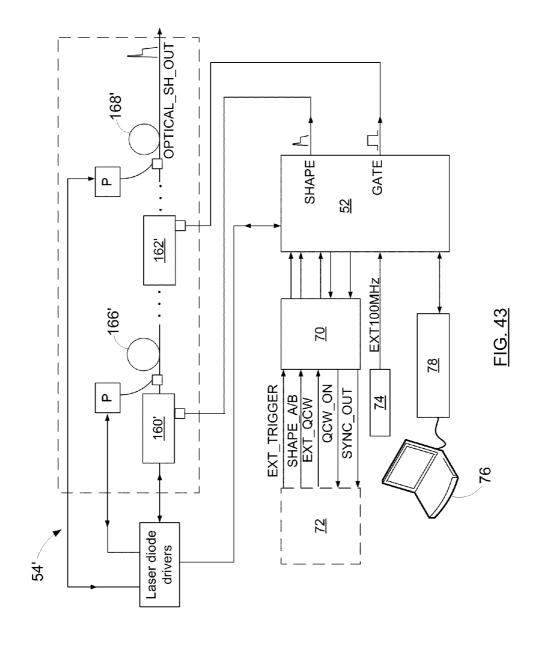

- FIG. 43 schematically illustrates an embodiment of the present invention using a seed laser diode operated in the pulsed regime and a modulator.

05 0,075,027 E

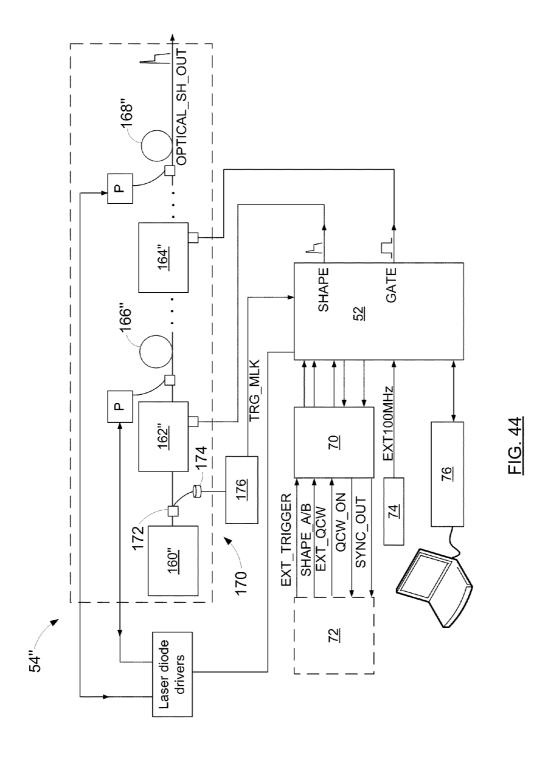

FIG. **44** schematically illustrates an embodiment of the present invention providing femtosecond or picosecond shaped pulse trains.

5

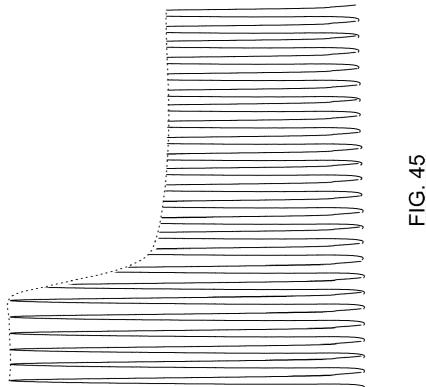

FIG. **45** is an illustration of a shaped picosecond pulse train generated with embodiments of the invention.

# DESCRIPTION OF PREFERRED EMBODIMENTS OF THE INVENTION

The present invention generally provides laser systems and 10 a digital pulse shaping module therefor enabling the versatile and adaptable generation of light pulses.

Laser systems according to embodiments of the invention may advantageously be tailored for any specific laser processing-based method or system that would take advantage of its pulse shaping capability. Numerous applications already exist or may be developed in several fields, such as selective ablation of neighboring microstructures in the semiconductor industry, memory repair, sophisticated laser trimming of glass, plastic or metal, medical applications such as selective cell or tissue alteration, etc. It will be understood that this list is non-exhaustive and that numerous other applications could benefit from laser systems using embodiments of the invention.

Overview of the Pulsed Laser System

Referring to FIG. 1, there is shown a pulsed laser system 50 which includes a digital pulse shaping module 52 controlling the laser oscillator of a pulsed laser source 54.

The pulsed laser system 50 may be embodied by any system apt to generate laser pulses and where the pulse shaping 30 functionality of a laser oscillator is controlled by one or more analog control signals. The expression "laser oscillator" is understood to refer to the portion of a laser source 54 which generates light pulses. The oscillator may include a laser cavity or alternatively be based on fluorescent emissions. The 35 oscillator may be part of a larger system including amplifying, beam shaping or any other optical components further defining the properties of the optical pulses generated by the oscillator. In preferred embodiments, the pulsed laser oscillator has a Master Oscillator, Power Amplifier (MOPA) laser 40 architecture, in which the control signals are used to drive gain-switched semiconductor lasers or high speed optical switches such as electro-optic modulators. Laser sources based on such oscillators, when incorporated into material processing systems, offer numerous advantages in terms of 45 throughput and processing windows over traditional Q-Switched technologies. However, one skilled in the art will understand that embodiments of the pulse shaping module 52 may also be used to provide control signals to Q-switched or other equivalent oscillators without departing from the scope 50 of the invention. Various exemplary embodiments of pulsed laser oscillator structures compatible with the present invention are given further below.

The digital pulse shaping module **52** controls the pulsed laser oscillator according to a digital input waveform. The 55 digital input waveform is a sequence of digital samples which may be defined or selected by a user, and which determine the resulting temporal shape of at least one pulse to be outputted by the pulsed laser source **54**. The digital pulse shaping module outputs a control shape signal adapted for controlling the 60 pulse laser oscillator to produce the desired pulses.

The control shape signal outputted by the digital pulse shaping module **52** is also herein referred to as the SHAPE signal. The digital pulse shaping module **52** has a first output port **68**, for outputting the SHAPE signal. Referring back to 65 FIG. **1**, the first port **68** may typically be connected to a MOD1 input of the pulsed laser source **54**, either for direct

6

modulation in the case of a seed laser diode or for driving an electro-optic modulator, whichever is internal to the architecture of the laser source 54. Also, for compatibility with different laser source architectures, the digital pulse shaping module 52 may optionally have a second output port 69 provide a control gate signal, hereinafter the GATE signal, that may, or may not, be required to be connected to a MOD2 input of the laser source. The GATE signal is preferably synchronized with the SHAPE signal and it can be used in some laser embodiments for gating or further shaping the optical pulse in-between optical amplifier stages. In a preferred embodiment of the invention, the amplitude of the GATE output is fixed, its length is user-adjustable in order to match the duration  $t_{sh}$  of the SHAPE output, and it always occurs after SHAPE by a delay dgt whose value is preferably user-adjustable. However, in alternative embodiments, the GATE signal may also be a shaped signal generated in a manner siminal to the SHAPE signal.

Under the effect of SHAPE, and optionally GATE, the laser source outputs a shaped optical signal OPTICAL\_SH\_OUT that is typically amplified by a fiber amplifier inside the source before getting to the target.

The pulsed laser system 50 is preferably adapted to interact with user equipment 72, which enables a user to interact and control the laser system according to desired operation parameters. A connector interface 70 preferably interfaces communication between the digital pulse shaping module 52 and the user equipment 72. The user equipment 72 may be embodied by any appropriate device or combination of devices such as, for example, a memory repair system, a photovoltaic cell scribing system, a micro-via drilling system or a laser surgery system.

Each electrical shape output by the digital pulse shaping module 52 on SHAPE may be triggered either by an internal or an external trigger signal. Preferably, the connector interface 70 provides an external trigger signal EXT\_TRIGGER to the digital pulse shaping module 52 in response to a trigger command from the user equipment 72. The connector interface 70 also optionally outputs a trigger synchronization signal SYNC\_OUT, having a predetermined timing relationship with respect to a light pulse emitted by the laser oscillator responsive to the external trigger signal EXT\_TRIGGER. Preferably, the trigger synchronization signal SYNC\_OUT has the same length t<sub>tr</sub> as EXT\_TRIGGER and occurs after the SHAPE output by a delay d<sub>so</sub> whose value may be fixed or user-adjustable. This delay d<sub>so</sub> enables SYNC\_OUT to occur quasi-simultaneously with the optical output of the laser source (OPTICAL\_SH\_OUT). The so-defined timing relationships between the EXT\_TRIGGER, SHAPE, GATE, SYNC\_OUT and OPTICAL\_SH\_OUT are all illustrated in FIG. 2.

In one embodiment of the invention, the pulsed laser system allows to switch between two input waveforms pre-selected by the user, hereinafter referred to as SHAPE\_A and SHAPE\_B. The connector interface 70 preferably provides a shape switching signal SHAPE\_A/B for switching dynamically the SHAPE output from one of the preselected waveforms to the other, in response to a shape selection command from the user equipment 72.

In one embodiment of the invention, when not triggered for pulse shape generation, the outputs SHAPE and GATE of the digital pulse shaping module **52** may default to a Quasi-Continuous Wave (QCW) signal, that is, a square-wave signal having a higher duty cycle than the typical duty cycle of the SHAPE signal, and an appropriate frequency, for example 100 MHz in the illustrated embodiment. The digital pulse shaping module **52** is preferably designed to switch dynami-

cally between the square-wave QCW mode and the pulse-shaping mode. Such switching action can be subject to pre-programmed conditions that will be described in sections below. It is to be noted that in the embodiment of FIG. 1, the connector interface 70 provides a QCW trigger signal 5 EXT\_QCW in response to a QCW command from the user equipment 72 to force QCW at the output of the digital pulse shaping module 52. A QCW flag QCW\_ON is preferably returned to the user equipment 72 through the connector interface 70 to acknowledge activation of the QCW mode.

Preferably, an oscillator external to the digital pulse shaping module **52** provides a start-up clock signal of 100 MHz at power-on. Other time-critical clock signals for the QCW and pulse shaping modes are generated inside the digital pulse shaping module **52**, as will be seen further below.

The digital pulse shaping module 52 includes a microcontroller 62 (see FIG. 3A) that can communicate with a host computer 76 through a communication port 78. The communication port 78 may for example be embodied by a RS-232, USB or Ethernet port or any equivalent thereto. In the illus- 20 trated embodiment, the host computer 76 is provided to command the digital pulse shaping module 52 to operate either in a SERVICE mode or in a USER mode, as will be explained in detail further below. The host computer 76 may be embodied by any appropriate device such as a general purpose com- 25 puter, driven by appropriate software. The software may also execute housekeeping functions in collaboration with the microcontroller in the digital pulse shaping module 52, such as controlling and monitoring laser pump drivers 80 associated with the pulsed laser source 54, and, if appropriate, 30 controlling and monitoring the extinction point of electrooptic modulators that might be present in the source.

In embodiments of the invention, all desirable laser functionalities such as digital control and monitoring of laser diodes, control of optical devices such as electro-optical 35 modulators, management of laser modes of operations (QCW/pulsed), management of communications with the host computer, etc. may advantageously be implemented in a very compact architecture, for example on a single PCB board. As this approach minimizes the number of individual 40 independent modules, many system functionalities can be easily implemented for a given application or laser system embodiment through modification of the Hardware Description Language HDL code alone without the need of addressing expensive hardware modifications.

Examples of the various components of pulsed laser systems according to embodiments of the invention will be explained in more detail in the following sections.

1. Digital Pulse Shaping Module

FIG. **3**A generally illustrates a digital pulse shaping mod- 50 ule **52** according to an embodiment of the invention.

The digital pulse shaping module 52 generally includes a clock generator 56 generating a plurality of phase-related clock signals at a same clock frequency, and a shape generator 58 outputting a digital shape signal DAC\_D corresponding to 55 the digital input waveform. The phase-related clock signals from the clock generator 56 are used as timing signals in the shape generator 58 in a double data rate configuration, hereinafter referred to as "DDR", as will be explained in detail further below. In one embodiment, the digital shape signal 60 DAC\_D from the shape generator 58 is either pulse shape data or quasi-continuous data. The pulse shaping module 52 further includes a Digital-to-Analog Converter **60**, hereinafter DAC, receiving the digital shape signal DAC\_D from the shape generator 58 and converting it into an analog shape signal DAC\_OUT. In the illustrated embodiment, the digital pulse shaping module 52 further includes a shape buffer

8

driver **64** receiving the analog shape signal DAC\_OUT from the shape generator **58** through the DAC **60** and generating the control shape signal SHAPE adapted for controlling the pulse laser oscillator. The microcontroller **62**, which, as mentioned above, is used for controlling the communications with the internal sub-systems of the laser source (pump drivers, etc.) and with the host computer, is finally provided.

The plurality of phase-related clock signals generated by the clock generator **56** include a Clock\_**0** signal, and Clock\_**90**, Clock\_**180** and Clock\_**270** signals respectively lagging a quarter of a period, half a period and three-quarters of a period behind the Clock\_**0** signal. In one embodiment, the phase-related clock signals are driven at 200 MHz. The clock generator **56** further preferably outputs a slow clock signal CLKD**4\_0** at 50 MHz, used mainly for clocking the slower elements in the design.

A frequency measurement module **96** is provided for measuring the frequency of the external trigger signal EXT\_TRIGGER from the connector interface.

The DAC **60**, may for example be embodied by the AD9736 model (trademark) from Analog Devices. The interface to the DAC **60** is preferably differential LVDS, 10-bit source-synchronous with the 200 MHz clock signal, DAC\_CLK. The data is input in double data rate into the DAC **60** on each rising edge and each falling edge of DAC CLK.

The analog output DAC\_OUT of the DAC 60 is either 100 MHz QCW or an analog pulse shape. This signal is input to the shape buffer driver 64 which is selected amongst devices appropriate for the external laser source. As such, the shape buffer driver 64 preferably has a very high slew rate and it is capable of driving a 50-Ohm load. This driver can use the Texas Instruments THS3102 amplifier (trademark), or a parallel combination of a few such amplifiers. Possibly also, the output of the shape buffer driver 64 may be transformer-coupled to the laser modulator. The resulting output signal is the SHAPE signal that is input to MOD1 of the laser source.

A low-jitter frequency synthesizer **61**, such as the IDT ICS8442 (trademark) with a 10 MHz crystal, outputs a 400 MHz clock signal to the DAC **60**. The DAC **60** divides this frequency down to 200 MHz to output the FPGA\_CLK signal used by the clock generator **56**.

In one embodiment, the shape generator **58** also outputs the PREDR\_GATE signal, either in QCW or pulse mode. This output has fixed amplitude and is also buffered similarly to the DAC\_OUT with a gate buffer driver **116**, for example a THS3102 type amplifier to drive the laser source. The resulting buffered output is the GATE signal that is input to MOD2 of the laser source.

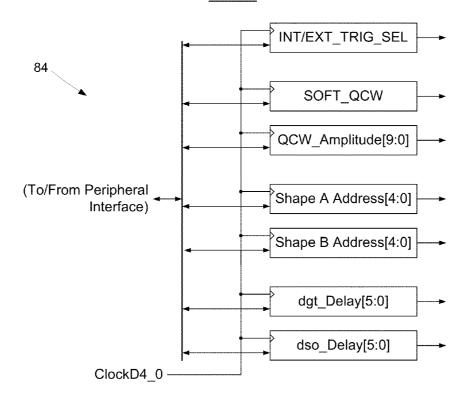

Peripherals such as a timer **82**, read/write registers **84**, dual-port shape memory buffers **86** and the like may additionally be provided as would be readily understood by one skilled in the art, all of which are preferably mapped on the bus of the microcontroller **62**. Detailed descriptions of these components according to examples of the implementation of the present invention are given further below.

Preferably, the microcontroller **62**, clock generator **56**, shape generator **58** and related peripherals are embedded on a high speed digital logic circuit **53**. In the different embodiments of the present invention, high speed digital logic circuits available in technologies such as ASIC or FPGA or off-the-shelves digital ICs and high speed Digital-to-Analog Converters (DAC) may be used to implement a pulse shaping capability and other desirable industrial laser functionalities resulting in a very efficient, low cost and agile laser system platform that can be easily tailored to several laser processing applications and laser architectures. This integrated approach promotes low jitter and generation of time delays with high

resolution for control of critical timings for the fast switching and synchronism of devices such as electro-optical modulators or semiconductor laser diodes.

In the preferred embodiment, the high speed digital logic circuit **53** is a FPGA, such as for example a Xilinx Virtex-2 5 Pro (trademark) which advantageously includes an embedded microcontroller. The advantages in implementing the FPGA-based architecture illustrated in FIG. **3**A are felt in terms of reliability, repeatability and versatility. Especially, it allows for creating a fully-synchronous platform where all the 10 timings, both inside the FPGA **53** and between the FPGA and the DAC **60**, are related to a single common timing reference, in this case clock input signal FPGA\_CLK. The timings, therefore, are homogeneous throughout the digital pulse shaping module.

Moreover, anyone familiar with FPGA technology and digital synchronous design is aware that the implementation described below is not limited to 200 MHz and that it allows for faster speed and, consequently, further temporal resolution in the optical shapes. To this end, the only requirement is 20 to configure the frequency synthesizer 61 to output signals of an appropriate frequency such as 500 MHz or 600 MHz to the DAC 60. The frequency of the input clock signal FPGA\_CLK shared by the DAC 60 and FPGA 53 therefore becomes 250 MHz or 300 MHz, which makes for a faster instrument. Of 25 course, if desired the digital pulse shaping module of embodiments of the invention may also be implemented in a slower regime.

Finally, it must be mentioned that the feasibility of the design described herein is subject to several good engineering practices such as appropriate usage of the software tools of the FPGA vendor, and also basic rules in the design of printed circuit boards such as proper part layout, impedance matching, skew analysis among bus signals, etc, as one skilled in the art will readily understand.

## 1.1 Shape Generator

In accordance with the embodiment of FIG. 3A, the shape generator 58 outputs in double data rate the following signals: the digital shape signal DAC\_D data and DAC clock signal DAC\_CLK which are both used as inputs to the high-speed DAC 60 to generate either a pulse shaping or QCW signal as the control shape signal SHAPE;

the gate signal PREDR\_GATE, for generating either QCW or fixed-amplitude pulse signal with adjustable width and delay as the control gate signal GATE;

the trigger synchronization signal SYNC\_OUT, with adjustable delay for synchronization with the output of optical pulse shapes from the laser source; and

the QCW flag QCW\_ON to flag or acknowledge that QCW is the current output mode on the SHAPE and GATE 50 output ports.

Referring to FIG. 3B, the shape generator 58 preferably includes the following sub-modules, embodiments of which will be described below with reference to the appended drawings:

a shape sub-module 57 (FIG. 14)

a gate sub-module 114 (FIG. 19)

a synchronization sub-module 130 (FIG. 24)

an internal/external trigger sub-module 85 (FIG. 8)

a QCW control sub-module 106 (FIG. 10)

a shape selection sub-module 142 (FIG. 11)

a delay control sub-module 128 (FIG. 12).

## 1.1.1 Shape Sub-Module

Referring to FIG. 14, there is shown a block diagram of the shape sub-module 57 according to a preferred embodiment of 65 the invention. In the illustrated embodiment, as will be explained in detail below, the DDR scheme is preferably

10

implemented through the use of parallely operating first and second shape state machines 100 and 102, respectively clocked by the Clock\_0 and Clock\_180 signals and each outputting a corresponding output shape D\_OUT. A shape DDR switch 104 alternatingly outputs the output shape D\_OUT from the first and second shape state machines 100 and 102 as the digital shape signal DAC\_D. The first and second shape state machines 100 and 102 therefore perform actions in parallel, but delayed by one half-clock period, or 2.5 ns in the 200 MHz frequency scheme. The signals they output at 200 MHz are forwarded to the shape DDR switch 104, which may for example be embodied by a DDR flip-flop in the I/O block (IOB) of the FPGA, in order to create an effective data flow of 400 MSample/s out of the system.

Each state machine 100 and 102 of the shape sub-module 57 may be operated in a shape mode, wherein the output shape corresponds to a selected predetermined waveform, or QCW mode, wherein the output shape is a quasi-continuous wave shape, depending on the command signal being asserted.

Preferably, by default, the shape state machines 100 and 102 are operated in QCW mode and signals QCW\_0, QCW\_180 force the output in 100 MHz QCW mode. Input signals QCW\_A\_0, QCW\_A\_180 determine the amplitude of the corresponding QCW signal and the outputted QCW\_ON signal flags or acknowledges the QCW output status to the connector interface (FIG. 1).

For each state machine 100 and 102, when the corresponding command QCW\_0, QCW\_180 is deasserted, the shape sub-module 57 operates in shape mode, and the output from each shape state machine is pulse shape data at every occurrence of the trigger signal pair TRIG 0, TRIG 180.

Preferably, each shape state machine 100 and 102 includes selecting means for selecting the digital input waveform from any one of a plurality of predetermined waveforms stored in 35 a corresponding shape memory buffer 86 (see FIG. 3A). For example, 32 pre-programmed predetermined waveforms may be available to choose from in the shape memory buffer, although, of course, any other appropriate number may alternatively be considered. For embodiments involving shape switching between shape A and shape B, each shape state machine 100 and 102 further includes shape switching means for dynamically switching the corresponding output shape between two of the predetermined waveforms stored in the shape memory buffer. In the illustrated embodiment of FIG. 14, SHAPE\_A\_ADDR\_\_0, SHAPE\_B\_ADDR\_0, SHA-PE\_A\_ADDR\_**180**, SHAPE\_B\_ADDR\_**180** addresses of the two preferred shapes among the 32 shapes available and SHAPE\_A/B\_0, SHAPE\_A/B\_180 actuate dynamic switching from shape A to shape B. The address of the selected shape, either shape A or shape B, is output to Shape\_Addr\_0, Shape\_Addr\_180 in order to read the shape data samples out of the shape memory buffers. The sequence of the shape sample addresses is output on Sample\_Addr\_0, Sample\_Addr\_180 while the sequence of the shape data 55 samples is read from Shape\_Data\_0, Shape\_Data\_180.

Still referring to FIG. 14, the shape sub-module 57 further preferably includes a DDR clock switch 112 clocked by the Clock\_90 and Clock\_270 signals providing a DAC clock signal DAC\_CLK as a clock to the double data rate port of the DAC. Since DAC\_D and DAC\_CLK are output through DDR flip-flops located in the IOB's of the FPGA, DAC\_CLK lags the DAC\_D data by a precise and repeatable delay of 1.25 ns in order to ensure reliable setup and hold times between the data and the clock seen by the DAC.

FIG. 15 illustrates the flow chart of the logic implemented in the shape state machines. As mentioned earlier, the output defaults to QCW unless the QCW input is deasserted, in

which case, a 32-sample shape is output to the DAC on each LOW-to-HIGH transition of the shape trigger.

FIG. 16 shows a timing diagram illustrating how the two shape state machines operate in parallel to output 100 MHz QCW. The shape state machines respectively output the 5 D\_OUT\_0 and D\_OUT\_180 sequences. In the preferred embodiment, the values in the sequences alternate between 0 and the 10-bit user-set QCW amplitude.

The DAC\_D output is generated by the DDR switch 104; on the rising edge of Clock\_0, the DDR switch outputs the <sup>10</sup> D\_OUT\_0 data, and on the rising edge of Clock\_180 immediately after, the DDR switch outputs the D\_OUT\_180 data.

The 100 MHz QCW square-wave output seen at DAC\_OUT results from the DAC\_D present at the DAC input on each rising and falling edge of DAC\_CLK. Note that the 15 diagram in FIG. 16 does not necessarily take into account possible pipelining latencies intrinsic to the DAC, but nevertheless, the diagram is valid for understanding the functional principle discussed herein.

The advantage of the double data rate approach is more 20 apparent in the generation of pulse shapes. FIG. 17 shows how the two shape state machines work in parallel to generate 16 consecutive sample addresses. Assuming that the 32 samples of a shape, S(0), S(1), S(2), ..., S(31), have been stored in the memory buffer according to an even-indexed/25 odd-indexed approach (see further below), when the triggers TRIG\_0, TRIG\_180 occur, identical addresses are generated on both Sample\_Addr\_0 and Sample\_Addr\_180, so that the double data rate sequence generated at DAC\_D is a well-ordered sequence that reproduces the shape sequence. This sequence is input in the DAC on rising and falling edges of DAC CLK.

In FIG. 17, a monotonically increasing pulse shape is represented at the output of the DAC. Since the double data-rate produces samples at each 2.5 ns, the effective output sampling rate is 400 MSPS.

Note that a shape may be defined to be 0 for all of its samples but the first one. Hence, a shape can be as short as 2.5 ns, or any length that is a multiple of 2.5 ns, up to 80 ns.

A feature of this embodiment of the invention is that it 40 provides the user with a very agile laser pulse shaping instrument capable of fast switching between a QCW mode and a pulse shaping mode, as well as fast switching between the two preferred shapes Shape A and Shape B when in pulse shaping mode.

FIG. 18 illustrates a typical sequence of output mode switching and shape switching. In time interval (1), the DAC outputs 100 MHz QCW since the QCW command input is asserted. The output goes to 0 when the QCW command is deasserted. At the beginning of time interval (2), the QCW command is deasserted and pulse shaping mode is enabled. The output remains to zero until a rising edge occurs on the TRIG input. This triggers the output of Shape A since the command Shape A/B is asserted for Shape A. The output of a shape is performed as a burst. No event at the QCW, the TRIG or the SHAPE A/B inputs can interrupt or alter the output sequence of the 32 shape samples. Once the 32 shape samples have been output, the output goes back to 0. At the beginning of time interval (3), pulse shaping is still enabled. Note that Shape A/B has changed state during the preceding time interval. Shape B is output when the next rising edge of TRIG occurs. Then the output goes back to 0. Since QCW has been asserted during output of shape B, in time interval (4) the output immediately reverts back to default QCW mode.

As can be seen from this example, in the preferred embodiment switching from QCW to pulse shaping occurs as soon as 65 QCW is deasserted, switching from pulse shaping to QCW occurs as soon as QCW is asserted at the end of a pulse shape.

12

Furthermore, switching between shapes is always accomplished as requested at the rising edge of TRIG following the end of the preceding pulse shape.

1.1.2 Gate Sub-Module

As mentioned above, the digital pulse shaping module preferably outputs a control gate signal GATE having a predetermined timing relationship with respect to the digital shape signal SHAPE. Referring to FIG. 19, the shape generator preferably includes a gate sub-module 114 generating an analog gate signal PREDR\_GATE. A gate buffer driver 116 (see FIG. 3A) receives the analog gate signal PREDR\_GATE and generates the corresponding digital control gate signal GATE.

In the illustrated embodiment, the gate sub-module 114 includes parallely operating first and second gate state machines 118 and 120, respectively clocked by the Clock\_0 and Clock\_180 signals and each outputting a corresponding gate output G\_OUT\_0 and G\_OUT\_180. First and second variable delay lines 122 and 124 are respectively associated with the first and second gate state machines 118 and 120, and impose a delay on the corresponding gate output G\_OUT\_0 and G\_OUT\_180. In this manner, a delayed gate output DG\_OUT\_0 and DG\_OUT\_180 is obtained from each delay line 122 and 124. A gate DDR switch 126 alternatingly outputs the delayed gate output DG\_OUT\_0 and DG\_OUT\_180 from the first and second delay lines 122 and 124 as the gate signal PREDR\_GATE.

In the preferred embodiment, the gate signal PRE-DR\_GATE outputted by the gate sub-module **114** is either QCW, or a fixed amplitude pulse signal with adjustable delay and width. Each pair of state machine and delay line **118-122** and **120-124** operate together in the 200 MHz domain. In one example of implementation of the invention, the variable delay lines **122** and **124** were configured for a minimum fixed delay value of 170 ns, plus and adjustable delay ranging from 5 to 160 ns in steps of 5 ns.

As shown in FIG. 19, the first and second gate state machines 118 and 120 are preferably controlled by asserting the QCW\_0, QCW\_180 input pair in order to force the outputs G\_OUT\_0, G\_OUT\_180 in 100 MHz fixed-amplitude QCW mode. When the QCW\_0, QCW\_180 input pair is deasserted, the outputs of the gate state machines 118 and 120 switch to a fixed-amplitude pulse mode synchronized with the occurrence of TRIG\_0, TRIG\_180.

1.1.3 Delay Control Sub-Module

Referring to FIG. 12, there is shown a gate control submodule 128 which is part of the shape generator according to one embodiment of the invention. FIG. 12 illustrates how dgt\_Delay and dso\_Delay, corresponding to software-selectable  $d_{gt}$  and  $d_{so}$  delay values in the timing diagram of FIG. 2, are propagated down to the DDR hardware of the digital pulse shaping module. The resulting DDR signal pairs are, respectively, DGT\_0, DGT\_180 for the  $d_{gt}$  delay and DSO\_0, DSO\_180 for the  $d_{so}$  delay.

Referring back to FIG. 19, the first and second gate state-machines 118 and 120 are preferably programmed so that the delayed outputs DG\_OUT\_0 and DG\_OUT\_180, once combined into the gate DDR switch 126, will produce a desired granularity of 2.5 ns in both the delay value  $d_{gt}$  and the pulse width  $t_{sh}$  of PREDR\_GATE. With the adjustable delay  $d_{gt}$ , and pulse width  $t_{sh}$  shown in FIG. 2, the DGT\_0, DGT\_180 is a 6-bit integer n such that

$170 \text{ } ns + (n \times 2.5) ns = d_{gs}$

and Gate\_Data\_0, Gate\_Data\_180 is an integer w such that  $(w \times 2.5) ns = t_{sh}$

The desired granularity can be achieved even if the temporal resolution of the signals output by the state machines and

the delay lines is 5 ns. The reason is that there is an intrinsic delay of one-half clock cycle, or 2.5 ns, between the pulse outputs of the state-machines and that the DDR flip-flops in the IOB of the FPGA have the ability to update their output at each 2.5 ns, or one-half clock cycle interval.

The first rule is to take only the five most-significant bits of DGT\_0, DGT\_180 to set the variable delay value of the delay lines. This is equivalent to delaying the outputs of the statemachines by (n\*×5) ns, where n\* is half the greatest even integer less than or equal to n. Following this rule, the pulse outputs of the gate state machines are always delayed by an even multiple of 2.5 ns, since the delay lines are clocked at 200 MHz and consequently, they have a single-tap delay of 5 ns

TABLE 1

| Rules for setting the W0, W180 output pulse widths |             |                        |                        |  |

|----------------------------------------------------|-------------|------------------------|------------------------|--|

| W                                                  | n           | <b>W</b> 0             | W180                   |  |

| odd                                                | even<br>odd | (w + 1)/2<br>(w - 1)/2 | (w - 1)/2<br>(w + 1)/2 |  |

| even                                               | even<br>odd | \ /                    | w/2                    |  |

Second, for a given combination of width w and delay n, the pulse width W0 and W180 output by, respectively, the first gate state machine 118 and the second gate state machine 120, are set according to the rules defined in Table 1 above.

Finally, for the case n odd, we further impose that there is 30 one wait state prior to outputting the pulse of width W0 at output G\_OUT\_0 of the first gate state machine 118.

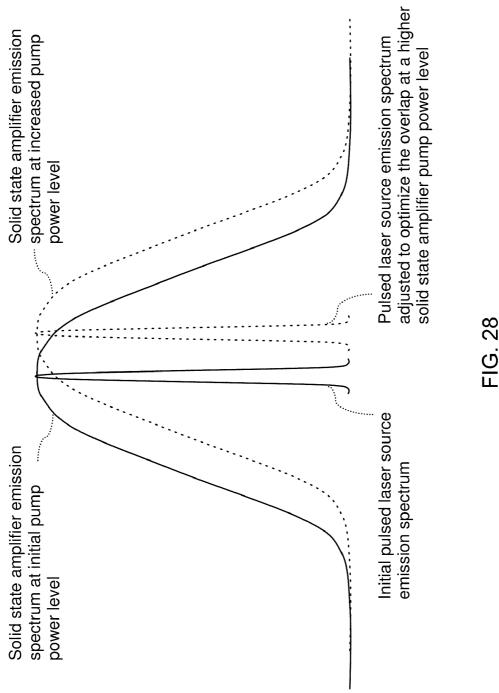

FIG. 20 to 23 are timing diagrams showing how applying these rules makes it possible to generate the PREDR\_GATE output with pulse width and delay values with the desired 35 granularity of 2.5 ns.

w odd, n even. Here we choose w=1 to output a pulse width of 2.5 ns, and n=2 to produce a delay  $d_{gr}$  which is an even multiple of 2.5 ns. Following the rules defined above, we have n\*=1 for a line delay which is  $(1\times5)$  ns, or  $(2\times2.5)$  ns; and 40 W0=1, W180=0, i.e., no pulse output by the second gate state machine 120. This is illustrated in FIG. 20, where we deliberately omit to represent the fixed offset of 170 ns of the delay lines. Note that even if a pulse of 5 ns is output by the first gate state machine 118, the PREDR\_GATE output lasts only 2.5 ns because the D\_180 input of the gate DDR switch 126 is always is 0. Further, it is fairly simple to demonstrate that for every other w odd, the pulse width  $t_{sh}$  is an odd multiple of 2.5 ns. Similarly, for every other n even, the delay  $d_{gr}$  is an even multiple of 2.5 ns.

w odd, n odd. Here, we set w=3 and n=3. Applying our rules, we have  $n^*=1$  for a line delay which is  $(1\times5)$  ns, or  $(2\times2.5)$  ns; and W0=1, W180=2. Also, since n is odd, there is one wait state at the output G\_OUT\_0. The result is illustrated and FIG. 21 and shows that the PREDR\_GATE pulse width is  $(3\times2.5)$  ns and that, with respect to the previous case illustrated in FIG. 20, an additional delay tap of 2.5 ns has now been added, which accounts for an odd-valued delay. For every other w odd, the pulse width  $t_{sh}$  is an odd multiple of 2.5 ns. Similarly, for every other n odd, the delay  $d_{gt}$  is an odd multiple of 2.5 ns. Particularly, for w=1, we get W0=0, W180=1 and it is readily seen that the width  $t_{sh}$  of PREDR\_GATE reduces to 2.5 ns.

w even, n even. Setting w=2, n=2. We get n\*=1, W0=1, W180=1. The result is illustrated and FIG. 22 and shows that 65 the delay is an even multiple of 2.5 ns and that the PRE-DR\_GATE pulse width is  $(2\times2.5)$  ns. For every other w even,

14

the pulse width  $t_{sh}$  is an even multiple of 2.5 ns. Similarly, for every other n even, the delay  $d_{ex}$  is an even multiple of 2.5 ns.

On the other hand, it is worth noting that for any n even delay, the first and second gate state machines 118 and 120 may be programmed to output the combination W0=1, W180=1, and then W0=0, W180=0, which will produce 100 MHz fixed-amplitude QCW on PREDR\_GATE when the input pair QCW\_0, QCW\_180 is asserted.

w even, n odd. Here, w=2 and n=3. Applying our rule, we have n\*=1 for a line delay which is  $(1\times5)$  ns, or  $(2\times2.5)$  ns; and W0=1, W180=1. Also, since n is odd, there is one wait state added at the output G\_OUT\_0. The result is illustrated in FIG. 23 and shows that the PREDR\_GATE pulse width is  $(2\times2.5)$  ns and that, with respect to the case illustrated previously in FIG. 22, an additional 2.5 ns delay tap has now been added, which accounts for an odd delay value. For every other w even, the pulse width  $t_{sh}$  is an even multiple of 2.5 ns. Similarly, for every other n odd, the delay  $d_{gt}$  is an odd multiple of 2.5 ns.

On the other hand, it is worth noting that for any n odd delay, the first and second gate state machines 118 and 120 may be programmed to output the combination W0=1, W180=1, then W0=0, W180=0, which will produce 100 MHz fixed-amplitude QCW on PREDDR\_GATE when the input pair QCW\_0, QCW\_180 is asserted.

1.1.4 Synchronization Sub-Module

Optionally, with reference to FIG. 24, the shape generator may include a synchronization sub-module 130 for generating the trigger synchronization signal SYNC\_OUT. Preferably, the output of the trigger synchronization signal output SYNC\_OUT is either a logical 0, or a fixed amplitude pulse signal with an adjustable delay. In the preferred embodiment, the synchronization generator 130 includes a first and second parallely operated synchronization state machines 132 and 134, and corresponding variable synchronization delay line 136 and 138, each pair of synchronization state machine and corresponding synchronization delay line being operated together in the Clock\_0 and Clock\_180 domains. In the preferred embodiment, the variable delay lines 136 and 138 are preferably configured for a minimum fixed delay value of 245 ns, plus an adjustable delay ranging from 5 to 160 ns in steps of 5 ns.

The first and second synchronization state machines 132 and 134 are preferably controlled by asserting the QCW\_0, QCW\_180 input pair in order to force the synchronization outputs SO\_OUT\_0, SO\_OUT\_180 into the logical 0 state.

When the QCW\_0, QCW\_180 input pair is deasserted, the synchronization outputs SO\_OUT\_0, SO\_OUT\_180 of the first and second synchronization state machines 132 and 134 switch to fixed-amplitude pulse mode, synchronized to the occurrence of TRIG\_0, TRIG\_180.

The first and second synchronization variable delay lines 136 and 138 impose a delay DSO\_0, DSO\_180 on the corresponding synchronization output SO\_OUT\_0, SO\_OUT\_180, thereby generating a delayed synchronization output DSO\_OUT\_0, DSO\_OUT\_180.

In accordance with the adjustable delay  $d_{so}$  and pulse width  $t_{rr}$  shown in FIG. **2**, the DSO\_**0**, DSO\_**180** is a 6-bit integer n such that

245  $ns+(n\times 2.5)ns=d_{so}$

and the duration  $t_{zr}$  of the pulse signal pair SO\_OUT\_0, SO\_OUT\_180 follows the duration of TRIG\_0, TRIG\_180 input pair.

A synchronization DDR switch 140 alternately outputs the delayed synchronization output DSO\_OUT\_0, DSO\_OUT\_180 from the first and second synchronization

state machines 132 and 134 as the trigger synchronization signal SYNC\_OUT. The first and second synchronization state machines 132 and 134 are programmed so that the delayed synchronization outputs DSO\_OUT\_0 and DSO OUT 180, once combined into the synchronization DDR switch 140, will produce the desired granularity of 2.5 ns in the delay value d<sub>so</sub> of SYNC\_OUT.

Referring back to FIG. 12, there is shown how the delay control module 128 provides the DSO\_0, DSO\_180 signal pair. In this embodiment, the first rule is to take only the five most-significant bits of DSO\_0, DSO\_180 to set the variable delay value of the delay lines. This is equivalent to delay the outputs of the state-machines by  $(n*\times5)$  ns, where n\* is half the greatest even integer less than or equal to n. Following this rule, the pulse output of the state-machine is always delayed by an even multiple of 2.5 ns.

The second rule is that for the case nodd, we further impose that there is one wait state prior to outputting the pulse at output SO\_OUT\_0 of the first synchronization state machine 20 132. As shown in FIG. 24, note that this condition will not apply to the instantiation of the second synchronization state machine 134, since its DELAY input is permanently tied to the logical 0 state.

In FIGS. 25 and 26, it is shown that applying these rules 25 makes it possible to generate the SYNC\_OUT output with pulse delay values at a desired granularity of 2.5 ns.

n even. Here, we set n=2. Applying our rules, we get  $n^*=1$ for a line delay which is  $(1\times5)$  ns, or  $(2\times2.5)$  ns. As shown in FIG. 25, this produces a delay  $d_{so}$  which is an even multiple of 2.5 ns and it is readily seen that for every other n even, the delay  $d_{so}$  is an even multiple of 2.5 ns.

n odd. Here, we set n=3. Applying our rule, we get n\*=1 for a line delay which is  $(1\times5)$  ns, or  $(2\times2.5)$  ns. Also, since n is odd, there is one wait state added at the output SO\_OUT\_0. The result is illustrated and FIG. 26 and shows that, with respect to the case illustrated previously in FIG. 25, an additional 2.5 ns delay tap has now been added which accounts for the delay  $d_{so}$  is an odd multiple of 2.5 ns.

## 1.1.5 QCW Control Module

The shape generator preferably includes a QCW control sub-module 106 which is illustrated in FIG. 10, and which provides the signals QCW\_0, QCW\_180, QCW\_A\_0, and 45 QCW\_A\_180. The QCW control sub-module 106 includes a QCW\_Amplitude register 108 and a SOFT\_QCW register 110. The output of the SOFT\_QCW register 110 defaults to asserting QCW, and is logically OR-ed with the EXT\_QCW hardware command and the FM\_QCW command generated 50 by the measurement of the frequency of the external trigger. All of EXT\_QCW, FM\_QCW and SOFT\_QCW must be deasserted for pulse shaping to be enabled.

As illustrated in FIG. 10, the hardware/software assertion control and amplitude settings of the QCW mode are propa- 55 gated down to the DDR QCW 0, QCW 180 and the QCW\_A\_0, QCW\_A\_180 signal pairs.

#### 1.1.6 Shape Selection Sub-Module

FIG. 11 illustrates a shape-selection sub-module 142 through which the Shape A/B shape select command and the 60 Shape A, Shape B software-selectable addresses are propagated down to the DDR hardware of the digital pulse shaping module. The resulting DDR signal pairs are, respectively, SHAPE\_A/B\_0, SHAPE\_A\_B\_180 for shape select, SHA-PE\_A\_ADDR\_0, SHAPE\_A\_ADDR\_180 for shape A 65 address and SHAPE\_B\_ADDR\_0, SHAPE\_B\_ADDR\_180 for shape B address.

16

Referring back to FIG. 3A, other components of a digital pulse shaping module 52 according to a preferred embodiment of the invention will now be described in more detail.

As suggested above, one skilled in the art will understand that other embodiments of the invention may be considered to provide the user with much higher output sampling rates, hence higher temporal resolution than what has been presented so far. One principle of interest put forward in the embodiments of the invention described above is that timecritical aspects of high-speed pulse shaping involve digital state-machines that output data to sequential elements located in the I/O blocks of the FPGA. The more recent FPGA components such as the Virtex-5 (trademark) from Xilinx now include sequential primitives like the IOSERDES in their I/O blocks. These allow DDR output at an effective rate higher than 1 GSPS. Although it might be necessary to store pulse shape data in memory in a different way than the one described above, the IOSERDES primitive might certainly be used in an embodiment of this invention that would achieve sub-nanosecond temporal resolution for QCW and pulse

## 1.2 Clock Generator

The clock generator 56 is preferably driven at power-on startup by the startup clock signal EXT100 MHz from the external oscillator 74 (see FIG. 1). A clock input signal, FPGA\_CLK, at 200 MHz in the preferred embodiment, is used as a timing reference to output the phase-related clock signals Clock\_0, Clock\_90, Clock\_180 and Clock\_270.

Preferably, the clock generator 56 also outputs a slow clock signal ClockD4\_0, at 50 MHz in the preferred embodiment. The slow clock signal CLKD4\_0 is used mainly for clocking the slower elements in the design, such as the microcontroller 62, the registers 84 and memory buffers 86.

In one embodiment, the clock generator 56 is based on a 35 Digital Clock Manager (DCM) primitive available in stateof-the-art FPGA components. The DCM is configured to output the five clock signals Clock 0, Clock 90, Clock 180, Clock 270 and ClockD4 0.

Referring to FIG. 4, Clock\_0, Clock\_90, Clock\_180 and an odd delay value. It is readily seen that for every other nodd, 40 Clock\_270 preferably have the same frequency as FPGA\_ CLK, namely 200 MHz in the preferred embodiment. ClockD4\_0 is at 50 MHz. Apart from a negligible latency, Clock\_0 is a copy of the 200 MHz input FPGA\_CLK. There is a strict phase relation among the outputs of the DCM: ClockD4\_0 is in phase with Clock\_0, Clock\_90 is lagging Clock\_0 by a quarter of a period, or 1.25 ns, Clock\_180 is lagging Clock 0 by half a period, or 2.5 ns and Clock 270 is lagging Clock\_0 by three quarters of a period, or 3.75 ns.

> The five outputs of the clock generator 56 are used to clock all the synchronous elements throughout the system, such as flip-flops, processor, or memories. Moreover, one skilled in the art and familiar with FPGAs knows that the software tools of the FPGA vendor take into account the phase relation between the different clock domains as defined in FIG. 4. As a consequence, the place-and-route of the design is performed iteratively so as to resolve any setup and hold time issue between synchronous elements, even if located in different clock domains, until reliable timing closure is achieved.

> The 200 MHz Clock\_0 and Clock\_180 are the main clocks used to generate either a QCW or pulse shape as the digital shape signal DAC\_D. The phase-relation between these two clocks is purposely set to one half-period in order to create a double data rate output for the samples sent to the DAC.

> The 200 MHz Clock 90 and Clock 270 are used to create the DAC clock signal DAC\_CLK for proper data setup and hold times in the source synchronous interface between the FPGA and the DAC.

As mentioned above, in the preferred embodiment, an external 100 MHz signal, EXT100 MHZ, is used for startup at power-on. Its only use is for clocking an elementary statemachine who releases system reset once (1) the DCM has locked on the FPGA\_CLK input and (2) the DCM outputs are 5 ready to clock the digital pulse shaping module 52.

#### 1.3 Frequency Measurement Module

The digital pulse shaping module 52 preferably includes a frequency measurement module 96 (see FIG. 1), which is preferably embodied by a state-machine having an internal counter clocked at 50 MHz. The frequency measurement module 96 asserts a QCW output flag FM\_QCW, to force the QCW output mode when the frequency of the external trigger signal EXT\_TRIGGER is outside of a pre-defined range.

Preferably, the frequency range of EXT\_TRIGGER for which the QCW output flag FM\_QCW is asserted is lower and upper bounded with hysteresis. For example, the transition diagram in FIG. 5 shows that the FM\_QCW output is asserted when the frequency of the EXT\_TRIGGER input 20 decreases below 88 KHz or increases beyond 1.1 MHz. Reciprocally, the FM\_QCW output is deasserted when the EXT\_TRIGGER frequency increases beyond 90 KHz or decreases below 1.0 MHz.

In the preferred embodiment, it is up to the user to activate 25 or de-activate the frequency monitoring function just-described. When monitoring is de-activated, no assertion of the FM\_QCW signal will occur.

#### 1.4 Microcontroller

The microcontroller **62** preferably has an embedded architecture as shown in FIG. 6. In the preferred embodiment, it is implemented in the FPGA around a CPU core 88, such as for example a Power PC 405 (trademark) from IBM. The platform of the microcontroller 62 is preferably tailored with the number and the type of peripherals needed by connecting 35 FPGA vendor-supplied peripheral cores to the CPU address/ data bus. First, a Program Memory core 90 is included for storing the programmed executable code for the CPU 88. A Timer core 92 is used for generating an internal shape trigger signal INT\_TRIGGER. A Peripheral Interface core 94 is con-40 nected to the CPU 88 to perform address decode and generate read/write control signals for data access to/from the command registers and the shape memory buffers. Communications with the laser pump drivers and the host are implemented with UART interfaces 95.

# 1.5 Command Registers and Control Signals

Referring to FIG. 7, there is shown a preferred embodiment of the command registers 84 for use in a digital shaping module according to FIG. 3. Preferably, the command registers 84 are embodied by read/write registers which are connected to the Peripheral Interface 94 of the microcontroller 62 (see FIG. 6). As such, they are clocked by the 50 MHz ClockD4\_0. The registers 84 are used for software-control of the QCW or pulse shape output modes on SHAPE, GATE and SYNC\_OUT outputs, together with the external hardware 55 86 according to an embodiment of the invention. The shape command signals EXT\_QCW, EXT\_TRIGGER and SHA-PE\_A/B (see FIG. 2).

In the section below, the role of the command registers is outlined, with respect to the main functional aspects such as triggering the pulse shapes, switching between QCW and 60 pulse shaping, and switching between shape A and shape B. It will be understood by one skilled in the art that the command registers 84 as described is given by way of example only. In addition, other command registers might be present in the platform for other useful purposes, but their description is not 65 essential to the understanding of the present invention.

Referring to FIG. 7, the registers are described as follows:

18

INT/EXT\_TRIG\_SEL: for selecting the external or the internally generated pulse trigger.

SOFT\_QCW: allows QCW output mode to be set by user software command.

QCW\_Amplitude[9:0]: 10-bit register for setting the amplitude of the 100 MHz OCW square wave signal.

Shape A Address[4:0]: 5-bit register for setting the address of Shape A among the 32 available shapes.

Shape B Address[4:0]: 5-bit register for setting the address of Shape B among the 32 available shapes.

dgt\_Delay[5:0]: 6-bit register for setting the delay value d<sub>set</sub> of GATE after SHAPE.

dso\_Delay[5:0]: 6-bit register for setting the delay value dg, of SYNC\_OUT after SHAPE.

The command registers are clocked by the 50 MHz ClockD4\_0 for read/write accesses by the CPU through the Peripheral Interface. For proper operation of the QCW or pulse shaping in double data rate mode, the state of the register must propagate down to the time-critical 200 MHz Clock\_0 and Clock\_180 clock domains altogether. This is accomplished by using cross-domain synchronization flipflops.

FIG. 8 shows an internal/external trigger sub-module 85 according to an embodiment of the invention, where synchronization flip-flops are used in the case of the external and internal pulse shape triggers, together with the INT\_EXT\_ TRIG\_SEL register.

First, as shown at the left-hand side of FIG. 8, the EXT TRIGGER connected to the pad of the FPGA is synchronized to the 50 MHz ClockD4\_0 right after entering the FPGA. This is done by using a dedicated input flip-flop located into the I/O block (IOB FF) of the FPGA.

The internally-generated trigger INT\_TRIGGER (FIG. 6) and the trig-select output of register INT/EXT\_TRIG\_SEL, by definition, are synchronized to ClockD4\_0. The trig-select output of the register orders a multiplexer to output either INT\_TRIGGER or the synchronized EXT\_TRIGGER. Since there is a well-defined phase-relationship between all clock signals, the TRIG output of the multiplexer is synchronous with respect to all three clocks ClockD4\_0, Clock\_0 and Clock\_180 and it can be readily propagated down to the TRIG\_0 TRIG\_180 signal pair through the synchronization flip-flops.

FIG. 9 illustrates that under the effect of the synchronization flip-flops, when a signal transition occurs in the ClockD4\_0 domain, it is followed by a corresponding transition of the signal pair in the Clock\_0, Clock\_180 domains. This typical dual-propagation principle is useful for the proper generation of the QCW or the pulse shapes at double data rate and it is used extensively throughout the practical implementation of this invention.

#### 1.6 Shape Memory Buffers

Referring to FIG. 13, there is shown a shape memory buffer memory buffer 86 stores a plurality of predetermined waveforms Shape\_Data, which are provided to the shape state machines of the shape sub-module upon selection.

The shape memory buffer 86 according to the illustrated embodiment includes two components, a pulse shape data buffer 143 storing the digital samples of the pulse shapes that are output on the SHAPE port, and a pulse duration data buffer 147 for storing the pulse durations  $t_{sh}$  of the pulses shapes (Refer to FIG. 2). This data is used to output the fixed-amplitude pulse signal on the GATE port. Each of data buffers 143 and 147 includes even and odd memory components 144, 146 and 148, 150.

The four memory components **144**, **146**, **148** and **150** are preferably dual-port type with their left port used for read/write accesses through the CPU's Peripheral Interface previously outlined with respect to FIG. **6**. The left port of these memories, therefore, is clocked at 50 MHz by ClockD**4\_0**, and it is used primarily for initializing the pulse shapes and the pulse durations.

In one embodiment, the shape memory buffer **86** is configured in the FPGA for a capacity of 32 shapes and 32 corresponding pulse durations. Each of the 32 pulse shapes is user-defined with 32, 10-bit samples, and each of the 32 pulse durations has a 6-bit value n, such that (n×2.5) ns is equal to the duration  $t_{sh}$  of the corresponding pulse shape.

The even pulse shape buffer component **144** of the pulse shape data buffer **143** contains the even-indexed samples of the shapes, while the odd pulse shape buffer component **146** contains the odd-indexed samples. More specifically, if a shape has 32 consecutive samples indexed as S(0), S(1), S(2), ..., S(30), S(31), then the 16 even-indexed samples S(0), S(2), ..., S(30) are stored in the even pulse shape buffer component **144** and the odd indexed samples S(1), S(3), ..., S(31) are stored in the odd pulse shape buffer component **146**.

This partitioning of the pulse shape data buffer **143** is defined for the practical implementation of the double data 25 rate output to the DAC. To this end, it is to be noted that the right port of the even pulse shape buffer **144** is clocked at 200 MHz by Clock\_0 and that the right port of the odd pulse shape buffer **146** is clocked at 200 Mhz by the shifted Clock **180**.

The right port of each of the pulse shape data buffer components **144** and **146** is read-only. It is connected to the shape generator **58** shown in FIG. **3**A and described above. Shape generator supplies the shape addresses Shape\_Addr\_0, Shape\_Addr\_180, the sample addresses Sample\_Addr\_0, Sample\_Addr\_180 and reads the data out of the memory.

The 5-bit Shape\_Addr\_0[4:0] is for selecting one shape among the 32 shapes available. In the even pulse shape buffer **144**, the 4-sample Shape\_Addr\_0[3:0] are for addressing each of the 16 even-indexed samples of the addressed shape. Data is read out of memory on the 10-bit bus Shape\_Data\_0. 40

Similarly, Shape\_Addr\_180[4:0] and Sample\_Addr\_180 [3:0] are for doing the equivalent on the odd pulse shape buffer 146. Data is read out of memory on the 10-bit bus Shape\_Data\_180.

The pulse duration data buffer 147 is similarly implemented in the even and odd pulse duration buffer components 148 and 150. These two buffers components 148 and 150 are provided two keep with the double data rate approach that is put forward in this embodiment of the invention. Hence, the even pulse duration buffer component 148 is clocked by 50 Clock\_0, while the odd pulse duration buffer component 150 is clocked by Clock 180.

Both pulse duration buffer components **148** and **150** preferably contain 32 values. For a given address, the 6-bit value stored at this address is the same in both even and odd components **148** and **150**, and is preferably a 6-bit integer n such that (n×2.5) ns is equal to the duration t<sub>sh</sub> of the corresponding pulse shape. As with the pulse shape data buffer **143**, the shape generator **58** of FIG. **3A** is responsible for generating the addresses for the pulse duration data buffer **147** and for reading its data output. FIG. **13** clearly illustrates that Shape\_Addr\_**0** will simultaneously address a given pulse shape data and its duration since the shape address seen by both buffer components **144** and **148** is the same. Similarly Shape\_Addr\_**180** simultaneously addresses a given pulse shape 65 data and its duration on the odd pulse shape component **146** and odd pulse duration component **150**.

20

Finally, it is to be noted that the data bus outputs of the even and odd components **148** and **150** have been named, respectively, Gate\_Data\_0 and Gate\_Data\_180, since these information are used in the generation of the fixed-amplitude pulse output on the GATE port of the digital pulse shaping module. 2. Service Mode

As mentioned above, in one embodiment of the invention the digital pulse shaping module operates either in a SER-VICE mode or in a USER mode.

Referring back to FIG. 1, according to one embodiment of the invention, in SERVICE mode, the software on the host computer 76 allows the user to define up to 32 arbitrary pulse shapes of his choice. Each shape is written as 32, 10-bit consecutive samples in the memory buffer of the digital pulse shaping module 52. Such fine granularity in the adjustable amplitudes of the sample enables very precise optical shapes to be output by the instrument. The software can select either the internal or the external EXT\_TRIGGER input to trig the shapes out of the digital pulse shaping module 52 to the laser source 54.

Each sample in a shape is 2.5 ns long so that a shape output by the digital pulse shaping module 52 has length varying between 2.5 and 80 ns. This allows internal or external triggering of the pulse shapes at a rate faster than 10 MHz.

Optionally, appropriate components such as a power splitter and a photodetector can be used in order to implement in the laser source 54 an output port for an analog electrical signal whose shape matches the optical shape output at OPTI-CAL\_SH\_OUT. This is the purpose of the FDBCK output appearing on the laser source 54, as illustrated in FIG. 1. By connecting this FDBCK signal to a display such as an oscilloscope, the user gets a visual feedback so that corrections can be sent to the digital pulse shaping module 52 to perform fine tuning in real-time of the optical pulse shaping at OPTI-SCAL\_SH\_OUT.

The software preferably on the host computer **76** also preferably allows the user to select two shapes among the 32 pulse shapes available. These are defined as Shape A and Shape B and they are provided for being output alternately on the SHAPE port under the action of the external SHAPE\_A/B signal input. Once selected by the user, Shape A and Shape B addresses are stored in the registers internal to the digital pulse shaping module **52**. This allows dynamic switching from Shape A to Shape B at a rate faster than 10 MHz.

Finally, the amplitude of the QCW output can be set by writing to a specific register, in case the register's default value is not suitable for the application.

It must be noted that other embodiments of this invention might implement pulse shaping with more than 10 bits per sample, more than 32 samples per shape, or more than 32 shapes. This simply is a matter of system architecture as it is defined in the HDL coding of the FPGA component.

In order to make the digital pulse shaping module **52** adaptable to different laser source architectures, the software on the host preferably allows the user to define the timing parameters for the GATE output.

Referring to FIG. 2, the value of the delay  $d_{gt}$  of GATE with respect to SHAPE is user-selectable by writing to a single register internal to the digital pulse shaping module 52. The allowed value for  $d_{gt}$  is in the range 170 ns up to 327 ns in steps of 2.5 ns.

On the other hand, the digital pulse shaping module **52** may provide a memory buffer for storing 32 values for the duration  $t_{sh}$  of GATE, as explained above. Each of these 32 values for  $t_{sh}$  must be equal to the duration of each of the 32 pulse shapes. When a given pulse shape of duration  $t_{sh}$  is triggered to be output on SHAPE, the corresponding fixed-amplitude

- -- - ,- - - ,-

pulse of equal duration  $t_{sh}$  is simultaneously triggered to be output on GATE, after a delay equal to  $d_{gr}$ . Accordingly with the allowed shape durations described above, the allowed value for  $t_{sh}$  is from 2.5 ns up to 80 ns in steps of 2.5 ns.

21

It must be noted that other embodiments of this invention 5 might implement different ranges of values for  $d_{gt}$  and  $t_{sh}$ . Moreover, the GATE output is not restricted to a fixed amplitude signal. In another embodiment of the invention, it could as well be designed and implemented as an arbitrarily shaped signal.

The software on the host computer **76** may also allow the user to set the value of the delay  $d_{so}$  after SHAPE for the SYNC\_OUT pulse (refer to FIG. **2**). The digital pulse shaping module **52** contains a single register for writing the value of  $d_{so}$ . The allowed value for this parameter is preferably in the 15 range 245 ns up to 403 ns in steps of 2.5 ns.

The SYNC\_OUT pulse has nominally the same duration  $t_{tr}$  as the EXT\_TRIGGER input. Other embodiments of this invention might implement different ranges of values for  $d_{so}$  and  $t_{rr}$ .

## 3. User Mode